m基于FPGA的多通道FIR滤波器verilog实现,包含testbench测试文件

1.算法仿真效果VIVADO2019.2仿真结果如下: 系统RTL结构如下: 2.算法涉及理论知识概要 多通道FIR(Finite Impulse Response)滤波器是一种在数字信号处理中广泛应用的线性时不变滤波技术,尤其适用于多通道音频、视频、图像等多维数据的处理。 单通道FIR滤波器可由其...

在FPGA上实现高通滤波器

在FPGA上实现高通滤波器的原理涉及数字信号处理的概念。高通滤波器用于去除低频信号,保留高频信号。以下是一个简单的FPGA高通滤波器的原理: 1. **延迟线**:为了实现滤波器功能,通常会使用延迟线存储输入信号的历史值。延迟线可以是一个简单的存储器单元,用于存储输入信号的多个时钟周期...

FPGA上实现低通滤波器

在FPGA上实现低通滤波器的原理涉及数字信号处理和滤波器设计的基本概念。以下是 FPGA 实现低通滤波器的基本原理: 1. **数字信号处理概念**:在FPGA上实现低通滤波器涉及将连续时间的模拟信号转换为离散时间的数字信号。数字信号处理涉及对这些离散信号进行处理和分析,其中滤波器是一...

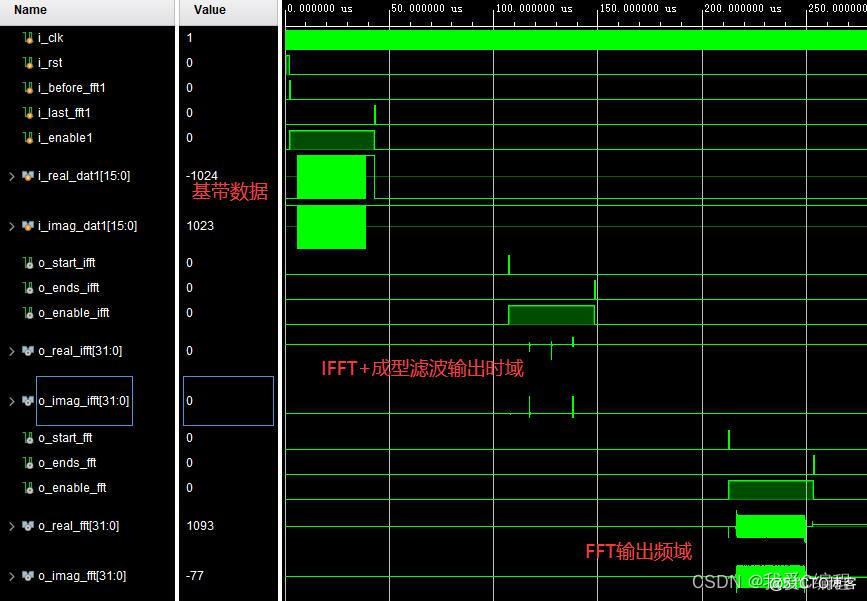

m基于FPGA的OFDM调制解调系统verilog实现,包括IFFT,FFT以及成型滤波器,包含testbench

1.算法仿真效果本系统进行了Vivado2019.2平台的开发,测试结果如下 整个OFDM结构如下: 2.算法涉及理论知识概要 正交频分复用(Orthogonal Frequency Division Multiplexing, OFDM)是一种多载波调制技术,其基本原理是将高速数据信号分成多个低速...

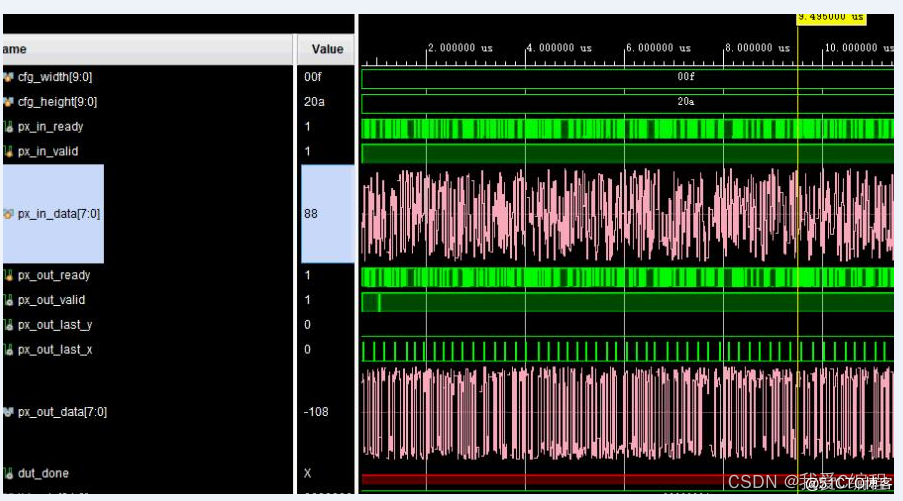

基于FPGA的LMS自适应滤波器verilog实现,包括testbench

1.算法仿真效果vivado2019.2仿真结果如下: 2.算法涉及理论知识概要 自适应算法是数字信号处理(DSP)的主体。它们被用于各种应用,包括声学回声消除、雷达制导系统、无线信道估计等。 自适应算法用于估算随时间变化的信号。有许多自适应算法,如递归最小二乘(RLS)和卡尔曼滤波,但最常用的是最...

基于FPGA的FIR低通滤波器verilog开发,包含testbench测试程序,输入噪声信号使用MATLAB模拟产生

1.算法仿真效果VIVADO2019.2/matlab2022a仿真结果如下: 运行matlab: 将matlab得到的数据文件保存到FPGA的project_13.sim\sim_1\behav\xsim路径,测试仿真时,可以自动调用matlab任意产生的测试数据。 rtl: 2.算法涉及理论知识...

基于FPGA的低通滤波器,通过verilog实现并提供testbench测试文件

1.算法仿真效果matlab2022a仿真结果如下:2.算法涉及理论知识概要 FIR(Finite Impulse Response)滤波器:有限长单位冲激响应滤波器,又称为非递归型滤波器,是数字信号处理系统中最基本的元件,它可以在保证任意幅频特性的同时具有严格的线性相频特性,同时其单位抽样响应是有...

基于FPGA的幅频均衡带通滤波器的设计

1.算法描述 数字通信系统中,由于多径传输、信道衰落等影响,在接收端会产生严重的码间干扰,增大误码率。为了克服码间干扰,提高通信系统的性能,在接收端需采用均衡技术。均衡是指对信道特性的均衡,即接收端的均衡器产生与信道特性相反的特性,用来减小或消除因信道的时变多径传播特性引起的码间干扰。幅频均衡就是在...

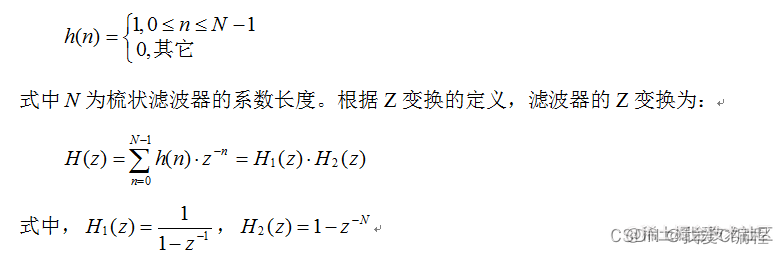

m基于FPGA的积分梳状CIC滤波器verilog设计

1.算法描述积分梳状滤波器,是指该滤波器的冲激响应具有如下形式:其物理框图如图所示:可见,CIC滤波器是由两部分组成:累积器H1和H2梳状滤波器的级联。 现若假设用N级CIC滤波器来代替,每一级的滤波器系数长度为R,每一级的差分延迟为M,抽取数为R,那么可以得到CIC抽取滤波器结构图: 可以看到,N...

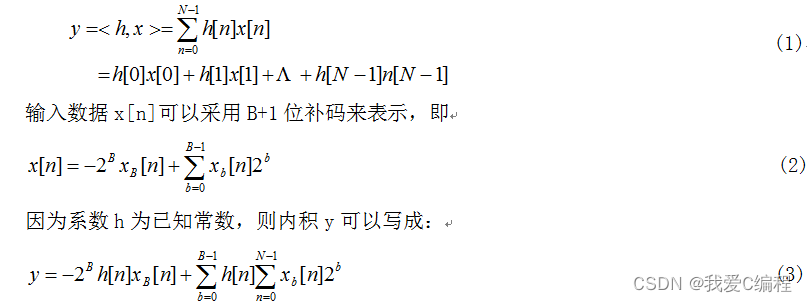

m基于FPGA的分布式FIR滤波器verilog设计,对比普通结构以及DA结构

1.算法描述 DA算法的主要特点是,巧妙地利用查找表将固定系数的MAC运算转化为查表操作,其运算速度不随系数和输入数据位数的增加而降低,而且相对直接实现乘法器而言,在硬件规模上得到了极大的改善。 对于FIR(有限长单位冲激响应)滤波器,其基本结构是一个分节的延时线,每一节的输出加权累加,得到滤波器的...

本页面内关键词为智能算法引擎基于机器学习所生成,如有任何问题,可在页面下方点击"联系我们"与我们沟通。

产品推荐

社区圈子