m基于FPGA的RS+卷积级联编译码实现,RS用IP核实现,卷积用verilog实现,包含testbench测试文件

1.算法仿真效果Vivado2019.2仿真结果如下: 2.算法涉及理论知识概要 级联码是一种通过将两种或多种纠错码结合使用来提高纠错能力的编码方案。在RS+卷积级联编码中,通常首先使用卷积码对原始数据进行编码,以增加冗余并提供一定的纠错能力。然后,将卷积码的输出作为RS码的输入进行进一步编码,以增...

[帮助文档] 读取多文件参数的方式

本文介绍在虚拟用户模式和RPS模式下,PTS读取多文件参数的方式。

m基于FPGA和IP核的RS编译码verilog实现,包含testbench测试文件

1.算法仿真效果本系统进行了Vivado2019.2平台的开发,测试结果如下: 2.算法涉及理论知识概要 在现代通信系统中,为了确保数据传输的可靠性,经常需要使用各种纠错编码技术。其中,里德-所罗门(Reed-Solomon, RS)码是一种非常强大的线性纠错码,特别适用于纠正多个随机符号错误。随着...

m基于FPGA的Hamming汉明编译码verilog实现,包含testbench测试文件,不使用IP核

1.算法仿真效果本系统进行了Vivado2019.2平台的开发,测试结果如下: 2.算法涉及理论知识概要 在现代数字通信和存储系统中,错误检测和纠正(Error Detection and Correction, EDC)机制是至关重要的。Hamming码,以其发明者Richard Hamming命...

[帮助文档] 磁盘分区文件数据同步测试出错

本文主要介绍在使用SMC迁移时,迁移任务出错提示“S10_* 磁盘分区文件数据同步测试出错”的问题描述、问题原因及其解决方案。

[帮助文档] 文件和输入框的最大限制

文件文件(CSV)最大支持60 MB。单行最大支持2万个字符。界面输入框URL输入框最大支持2083个字符。Body输入框最大支持65535个字符。

[帮助文档] 使用HAR文件快速开始压测

HAR(HTTP Archive format)是用来记录HTTP请求和响应信息的标准格式文件,Google Chrome、Charles、Fiddler等工具均支持导出HAR格式文件。您可以使用HTTP Archive Format(.har)导入场景功能将录制的HTTP流量导入PTS压测场景。本...

[帮助文档] 微服务压测中的参数文件URL和动态参数调用规则

本文介绍微服务压测中的参数文件URL和动态参数调用规则。

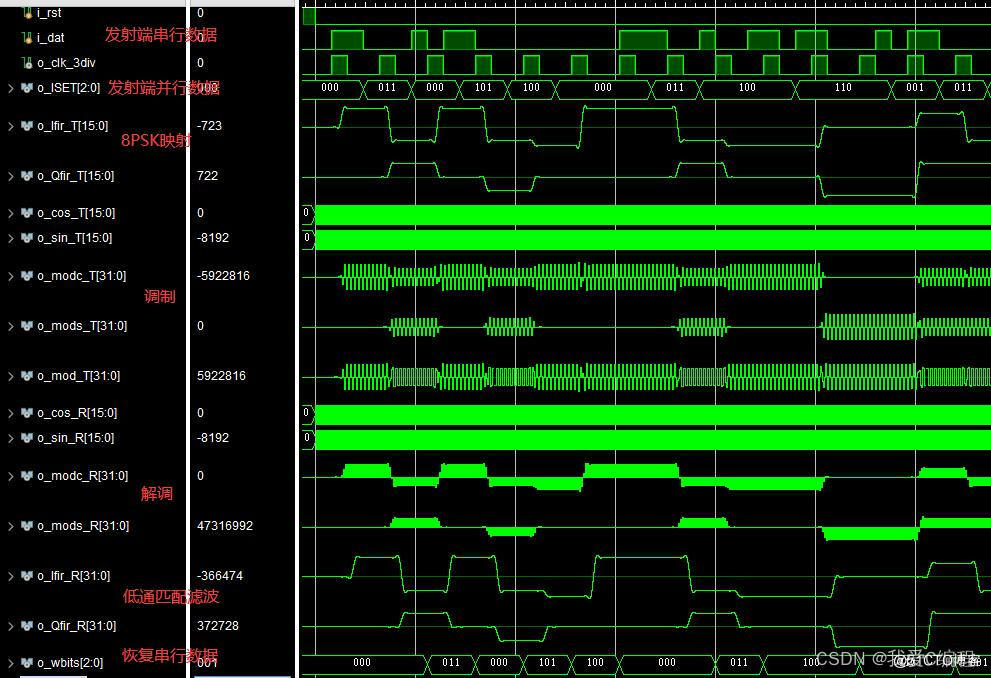

m基于FPGA的8PSK调制解调系统verilog实现,包含testbench测试文件

1.算法仿真效果vivado仿真结果如下: 借助matlab看8PSK的星座图: 2.算法涉及理论知识概要 随着通信技术的不断发展,相位调制技术因其高频谱效率和抗干扰能力而广泛应用于无线通信系统中。其中,8PSK(8相位相移键控)作为一种高阶调制方式,具有更高的频谱效率和更强的抗干扰能力,因此备受关...

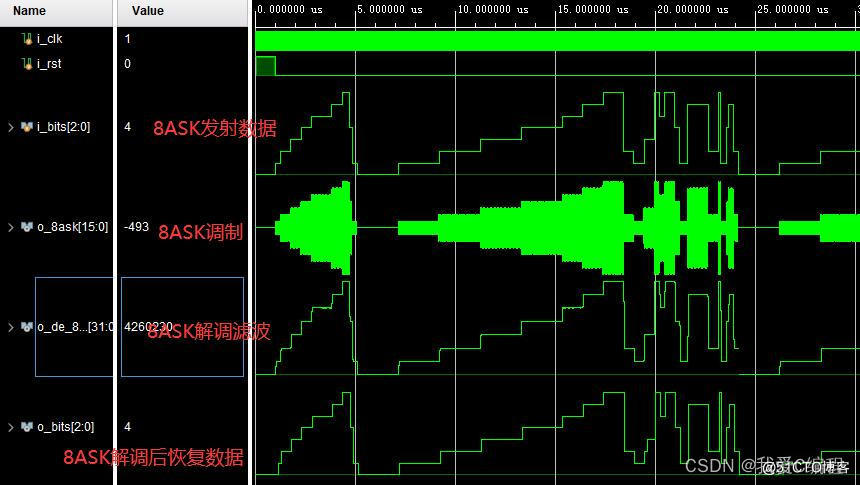

m基于FPGA的8ASK调制解调系统verilog实现,包含testbench测试文件

1.算法仿真效果本系统Vivado2019.2平台开发,测试结果如下: rtl结构如下: 2.算法涉及理论知识概要 8ASK(八进制振幅键控)是一种数字调制技术,它是ASK(振幅键控)的一种扩展形式。在8ASK中,信号的振幅被调制成八个不同的级别,每个级别代表三个二进制位的信息。因此,与2ASK和4...

本页面内关键词为智能算法引擎基于机器学习所生成,如有任何问题,可在页面下方点击"联系我们"与我们沟通。

测试文件相关内容

- 测试文件验证

- 计算测试文件

- verilog测试文件

- 检测测试文件

- 设置测试文件

- fpga verilog包含testbench测试文件

- 文件共享测试

- 文件测试

- fpga测试文件

- 网盘相册测试文件

- 测试下载文件

- fpga编译码测试文件

- verilog包含testbench测试文件

- 算法实现测试文件matlab辅助验证

- mybatis文件测试

- fpga调制解调系统verilog testbench测试文件

- fpga包含testbench测试文件

- 测试文件存在

- ai测试文件

- 语法测试文件

- 测试目录文件

- 测试知识点文件

- 测试xml文件

- 测试面试题文件

- hadoop测试文件目录

- 测试参数文件

- 日志文件测试

- .net测试文件

- ios测试文件

- maven测试文件

- 测试文件下载

- google测试扩展文件安装包验证

- 测试文件信息

- dom文件测试