m基于FPGA的Alamouti编码verilog实现,包含testbench测试文件

1.算法仿真效果 本系统进行了Vivado2019.2平台的开发,结果如下: 2.算法涉及理论知识概要 在无线通信领域,多天线技术是提高系统容量和可靠性的关键手段之一。Alamouti编码是空时编码(STC)的一种,它为两发射天线的系统提供了一种全速率、全分集的简单编码方案。而空频分组编码(SFBC...

【FPGA】Verilog 编码实现:与非门 | 或非门 | 异或门 | NAND/NOR/XOR 行为验证

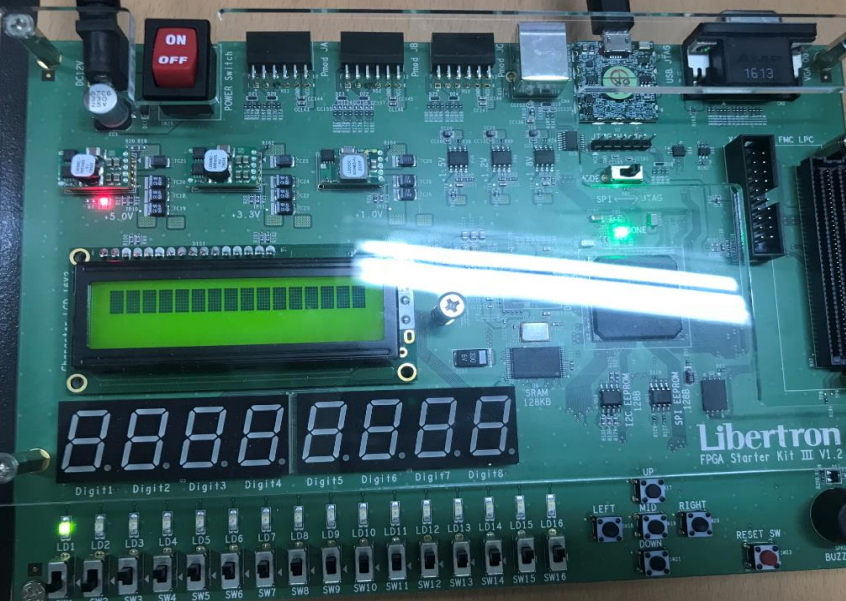

写在前面:本章主要内容为了解和确认 NAND/NOR/XOR 门的行为,并使用Verilog实现,生成输入信号后通过模拟,验证每个门的操作,并使用 FPGA 来验证 Verilog 实现的电路的行为。Ⅰ. 前置知识0x00 与非门(NAND)如果所有输入均为High (1),则输出为L...

【FPGA】基本实验步骤演示 | Verilog编码 | 运行合成 | 设备/引脚分配 | 综合/实施 | 设备配置 | 以最简单的逻辑非为例

写在前面:本章的目的是让你理解与门、或门和非门的行为,并使用 Verilog 语言实现多输入与门、或门和非门。在生成输入信号之后,你需要通过模拟来验证这些门的操作,并使用 FPGA 来验证 Verilog 实现的电路的行为。0x00 引入:与门、或门与非门构成数字系统电路的最基本元素,以集成电路的形...

NGcodec谈FPGA编码与HEVC和AV1

随着HEVC、AV1等更复杂算法的Codec份额逐步增长,实现高质量视频编解码需要硬件支持,软件的方式无论在服务器端和移动端都非最佳的方案。FPGA专用芯片能够降低延迟和成本。在NAB 2018大会上,资深多媒体技术咨询师Jan Ozer对Ngcodec的CEO Oliver Gunasekara进...

本页面内关键词为智能算法引擎基于机器学习所生成,如有任何问题,可在页面下方点击"联系我们"与我们沟通。

产品推荐

社区圈子