m基于FPGA的多通道FIR滤波器verilog实现,包含testbench测试文件

1.算法仿真效果VIVADO2019.2仿真结果如下: 系统RTL结构如下: 2.算法涉及理论知识概要 多通道FIR(Finite Impulse Response)滤波器是一种在数字信号处理中广泛应用的线性时不变滤波技术,尤其适用于多通道音频、视频、图像等多维数据的处理。 单通道FIR滤波器可由其...

基于FPGA的FIR低通滤波器verilog开发,包含testbench测试程序,输入噪声信号使用MATLAB模拟产生

1.算法仿真效果VIVADO2019.2/matlab2022a仿真结果如下: 运行matlab: 将matlab得到的数据文件保存到FPGA的project_13.sim\sim_1\behav\xsim路径,测试仿真时,可以自动调用matlab任意产生的测试数据。 rtl: 2.算法涉及理论知识...

m基于FPGA的分布式FIR滤波器verilog设计,对比普通结构以及DA结构

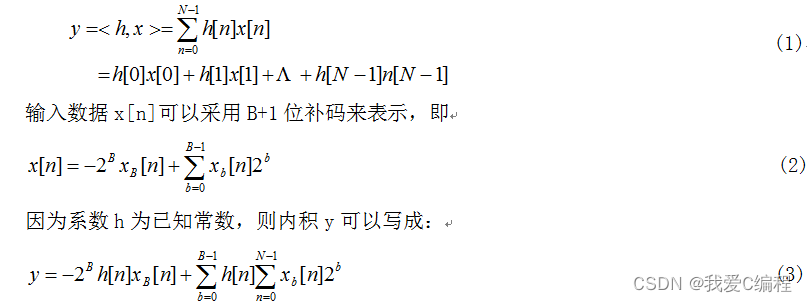

1.算法描述 DA算法的主要特点是,巧妙地利用查找表将固定系数的MAC运算转化为查表操作,其运算速度不随系数和输入数据位数的增加而降低,而且相对直接实现乘法器而言,在硬件规模上得到了极大的改善。 对于FIR(有限长单位冲激响应)滤波器,其基本结构是一个分节的延时线,每一节的输出加权累加,得到滤波器的...

m基于FPGA的多级抽取滤波器组verilog设计,包括CIC滤波,HB半带滤波以及DA分布式FIR滤波

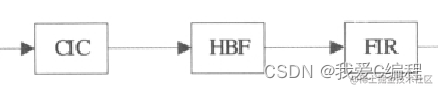

1.算法描述 数字下变频中的低通滤波器是由多级抽取滤波器组实现的。信号的同相分量和正交分量再分别经由积分梳状滤波器(CIC)、半带滤波器(HB)和有限长单位脉冲响应(FIR)滤波器构成的多级抽取滤波器组进行滤波和降采样处理,再将产生的正交基带信号I (n)、Q (n)送到通用DSP处理器,进行信号识...

FPGA的FIR抽取滤波器设计

摘 要:本文介绍了FIR抽取滤波器的工作原理,重点阐述了用XC2V1000实现FIR抽取滤波器的方法,并给出了仿真波形和设计特点。 关键词:FIR抽取滤波器;流水线操作;FPGA 用FPGA实现抽取滤波器比较复杂,主要是因为在FPGA中缺乏实现乘法运算的有效结构,现在,FPGA中集成了硬件乘法器...

本页面内关键词为智能算法引擎基于机器学习所生成,如有任何问题,可在页面下方点击"联系我们"与我们沟通。

产品推荐

社区圈子