FPGA项目五:数码管动态扫描(下)

第四节 综合和上板4.1 新建工程打开软件 Quartus Ⅱ,点击“File”下拉列表中的 New Project Wzard…新建工程选项,如下图所示。随后会出现 Quartus 新建工程介绍,如下图所示,直接点击“Next”。此时会出现工程文件夹、工程名、顶层模块名设置界面,如图 3.5-13...

FPGA项目五:数码管动态扫描(中)

确定完两个计数器后来思考输出信号 seg_sel 的变化。根据信号波形图得知,第 1 秒时 FPGA输出值为 8’hfe;第 2 秒时输出值为 8’hfd;以此类推,在第 8 秒时输出值为 8’h7f。设计中使用 cnt1来表示第几个 1 秒,即 cnt1==0 的时候,输出值为 8’hfe&...

FPGA项目五:数码管动态扫描(上)

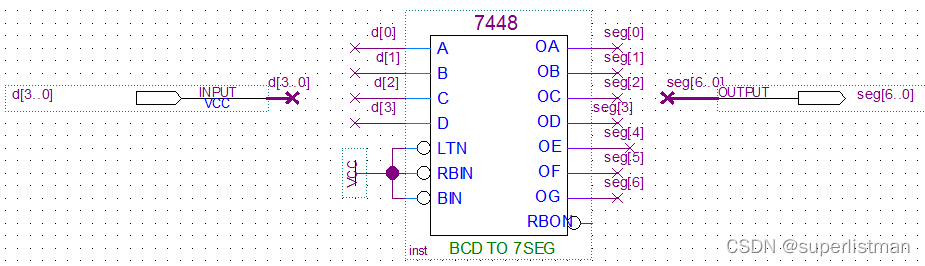

第五章 数码管动态扫描第 1 节 项目背景led 数码管(LED Segment Displays)是由多个发光二极管封装在一起的器件,这些二极管组成“8”字型,在内部完成引线连接,只引出它们的各个笔划和公共电极。一般来说,led> 数码管常用段数为 7 段,如下图中所示的 a、b、c、d、e...

实验三 基于FPGA的数码管动态扫描电路设计 quartus/数码管/电路模块设计(下)

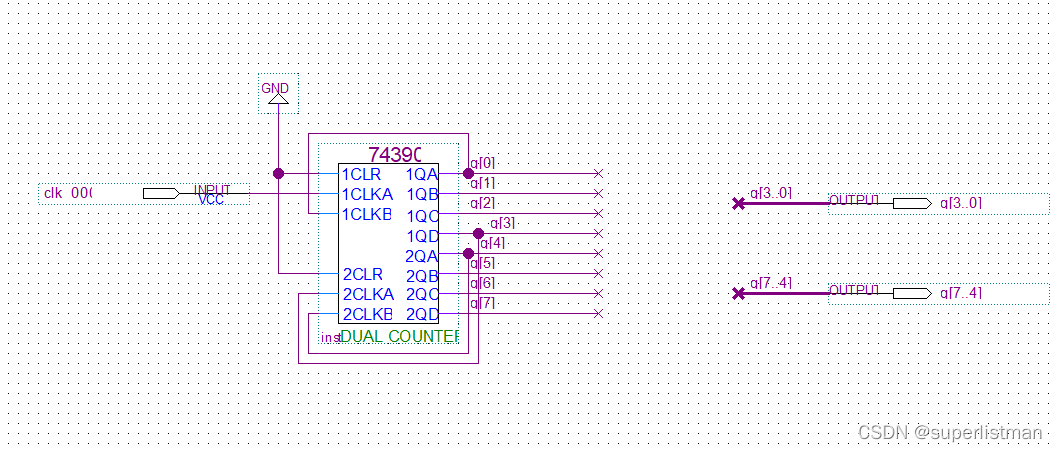

基本任务3:利用FPGA硬件平台上的6位数码管显示模100计数结果(以1S为节拍);1、电路设计(1)实验三就有一些复杂了。要实现模100计数结果,我们首先要有一个模100计数器。cnt100(2)第二个新模块是sec_select模块,之所以这么命名和设计...

实验三 基于FPGA的数码管动态扫描电路设计 quartus/数码管/电路模块设计(上)

实验三 基于FPGA的数码管动态扫描电路设计源文件的链接放在最后啦实验目的:(1) 熟悉7段数码管显示译码电路的设计。(2) 掌握数码管显示原理及静态、动态扫描电路的设计。实验任务:(1) 基本任务1:利用FPGA硬件平台上的4位数码管做静态显示,用SW0-...

每个FPGA 包含了多少个并行的数据解压缩引擎和几个扫描引擎?

每个FPGA 包含了多少个并行的数据解压缩引擎和几个扫描引擎?

本页面内关键词为智能算法引擎基于机器学习所生成,如有任何问题,可在页面下方点击"联系我们"与我们沟通。

产品推荐

社区圈子