FPGA(3)--VHDL及原理图--4位全加器

文章目录一、实验目的二、实验内容三、实验设计五、实验思考与总结一、实验目的掌握例化语句的使用方法,掌握使用程序文本和原理图结合方法设计电路,掌握利用包含算术操作符的重载函数的使用。二、实验内容首先用VHDL语言设计1位全加器,仿真验证其正确性,并将其封装成一个元件;设计串行4位加法器的电路,调用1位...

FPGA(2)--例化语句--1位全加器

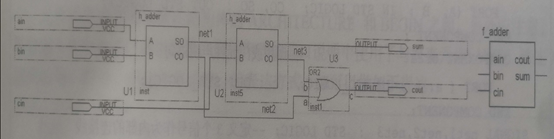

文章目录一、实验目的二、实验内容三、实验设计四、实验结果及仿真一、实验目的熟悉元件封装方法,掌握层次化电路设计方法;掌握VHDL例化语句的设计方法。二、实验内容1.用VHDL语言设计1位全加器,其中仅就半加器实体进行例化声明及端口映射语句,或运算直接调用运算函数。通过编译、仿真验证功能正确性。2.就...

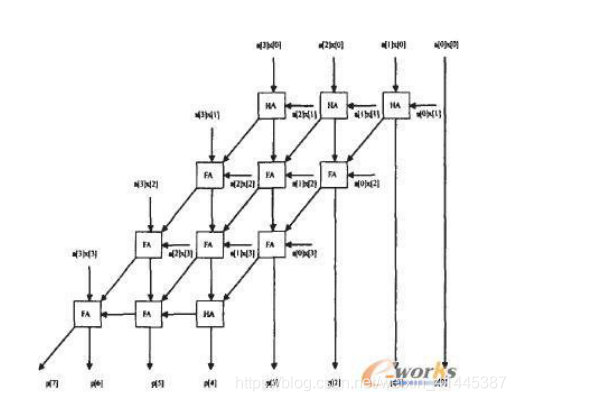

FPGA-阵列乘法器的设计(利用全加器 基于CRA阵列乘法器)

在计算机中,乘法是数字信号处理中的重要角色。 四位无符号数相乘的手算运算可以提炼出最简单的乘法器的计算算法,利用手算乘法的思想,算出每次的部分积然后求和。这样的方法思想较为容易理解前面的(FPGA-定点乘法器)已经给出具体的代码的设计,代码中设计的是4位,则...

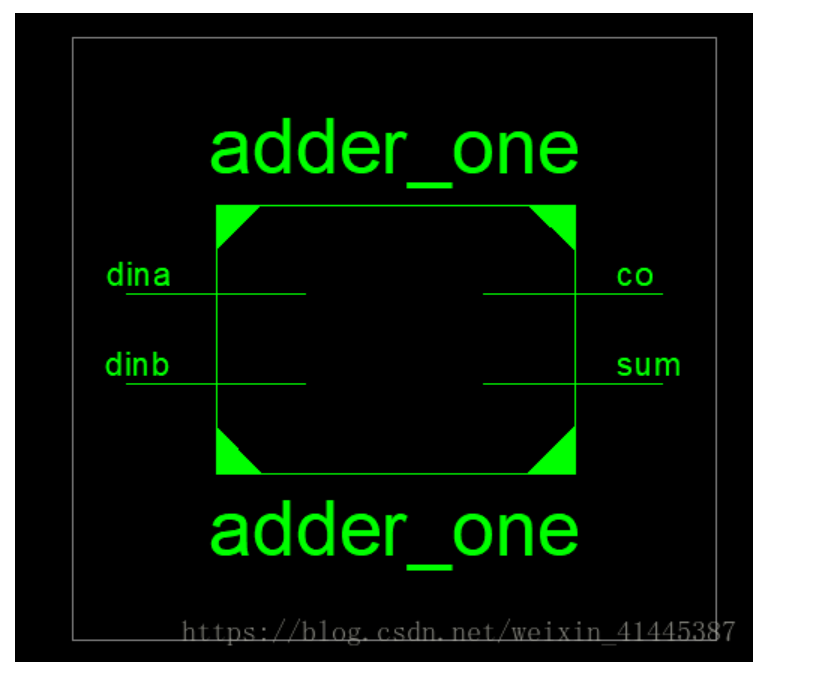

FPGA-基本知识 设计一个一位(四位)半加器和一位(四位)全加器

使用ISE设计一个加法器(半加器):dina (输入)dinb(输出) co(进位输出)sum(和输出)代码如下:module adder_one(dina,dinb,sum,co ); input dina; ...

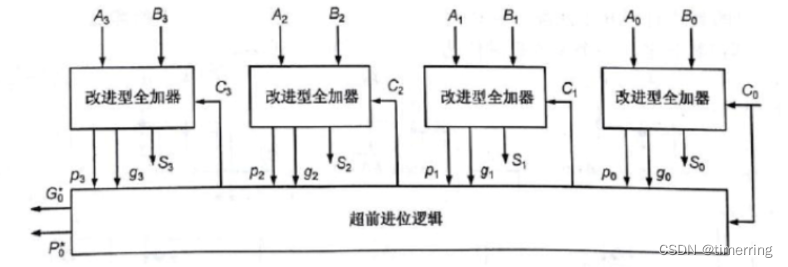

FPGA设计超前进位与8421-BCD码全加器

设计一个16位二进制超前进位全加器模块实验内容与原理说明本实验设计一个16位二进制的超前进位全加器模块,用来实现16位二进制的加法,超前进位加法器的结构如下图。下图为一个四位超前进位加法器的结构图。信号经过pi和gi产生一级时延,经过计算C产生一级时延,则A,B输入一旦产生,首先经过两级时延算出第...

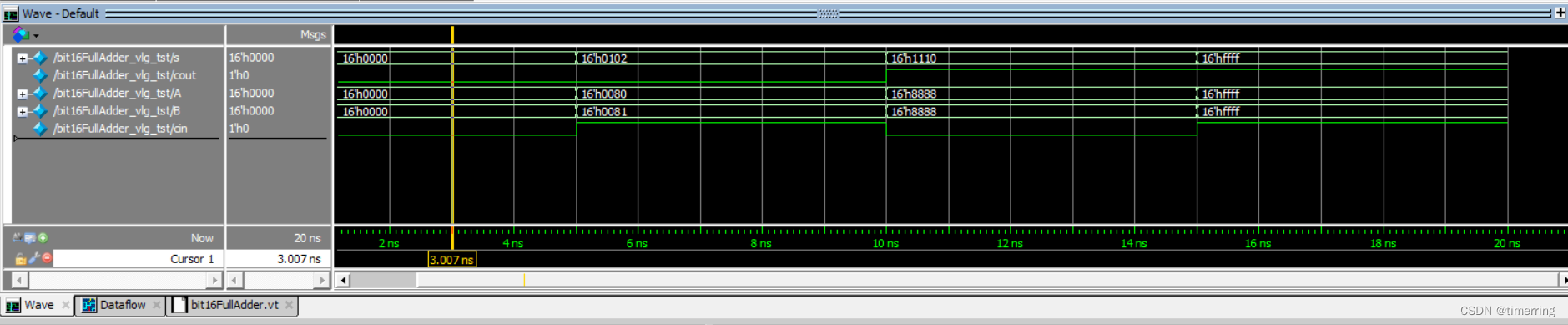

FPGA设计16位二进制全加器模块

【实验要求】 实验内容与原理说明(包括框图、逻辑表达式和真值表)。实验模块程序代码(设计模块Design Block)和激励代码(激励模块Test Bench)。仿真波形图。综合得到的门级电路图。实验结果分析及思考。每一次报告用Word文档提交,文件名:姓名_班级_第几次实验_学号。【...

本页面内关键词为智能算法引擎基于机器学习所生成,如有任何问题,可在页面下方点击"联系我们"与我们沟通。

产品推荐

社区圈子