FPGA - 7系列 FPGA内部结构之SelectIO -09- 高级逻辑资源之IO_FIFO

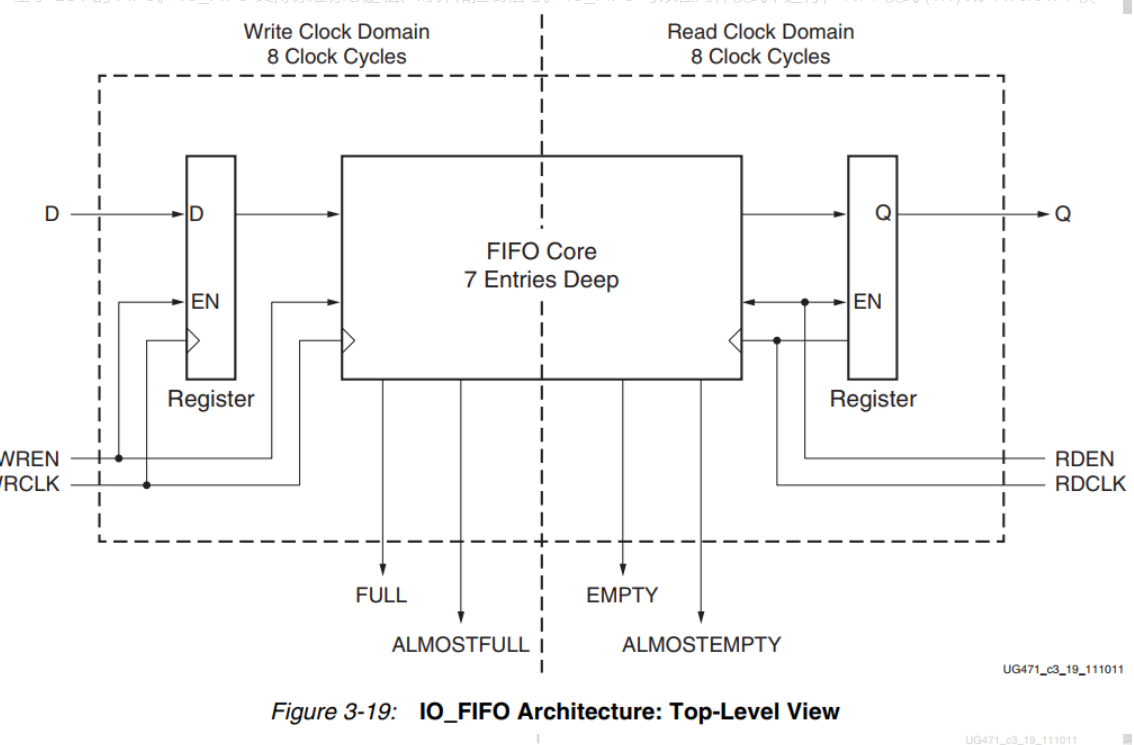

前言本文节选UG471的第三章,进行整理翻译,用于介绍高级SelectIO逻辑资源内部的IO_FIFO资源。IO_FIFO 概述7系列器件在每个 I/O bank 中都有浅层 IN_FIFO 和 OUT_FIFO(统称为 IO_FIFO)。 尽管这些 IO_FIFO 是专门为内存应用设计的,但它们也...

FPGA - 7系列 FPGA内部结构之SelectIO -08- 高级逻辑资源之OSERDESE2(二)

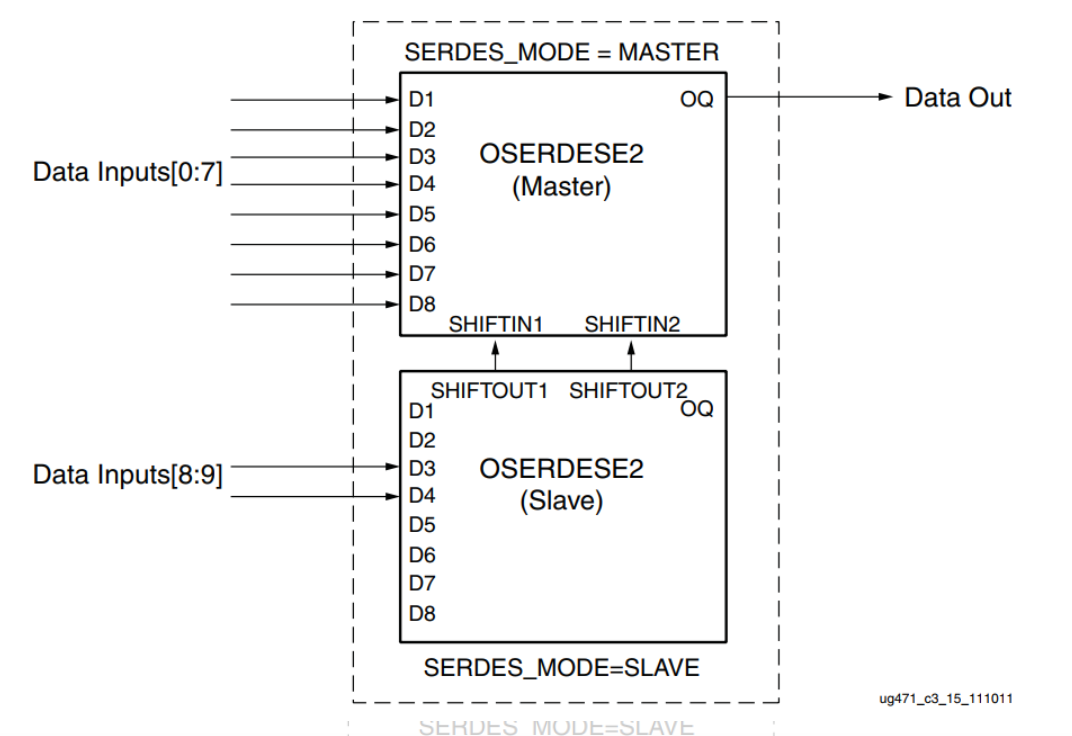

OSERDESE2 宽度扩展OSERDESE2 模块用于构建大于 8:1 的并串转换器。 在每个 I/O 块中都有两个 OSERDESE2 模块; 一主一从。 通过将主 OSERDESE2 的 SHIFTIN 端口连接到从 OSERDESE2 的 SHIFTOUT 端口,并行到串行转换器可以扩展到高...

FPGA - 7系列 FPGA内部结构之SelectIO -08- 高级逻辑资源之OSERDESE2(一)

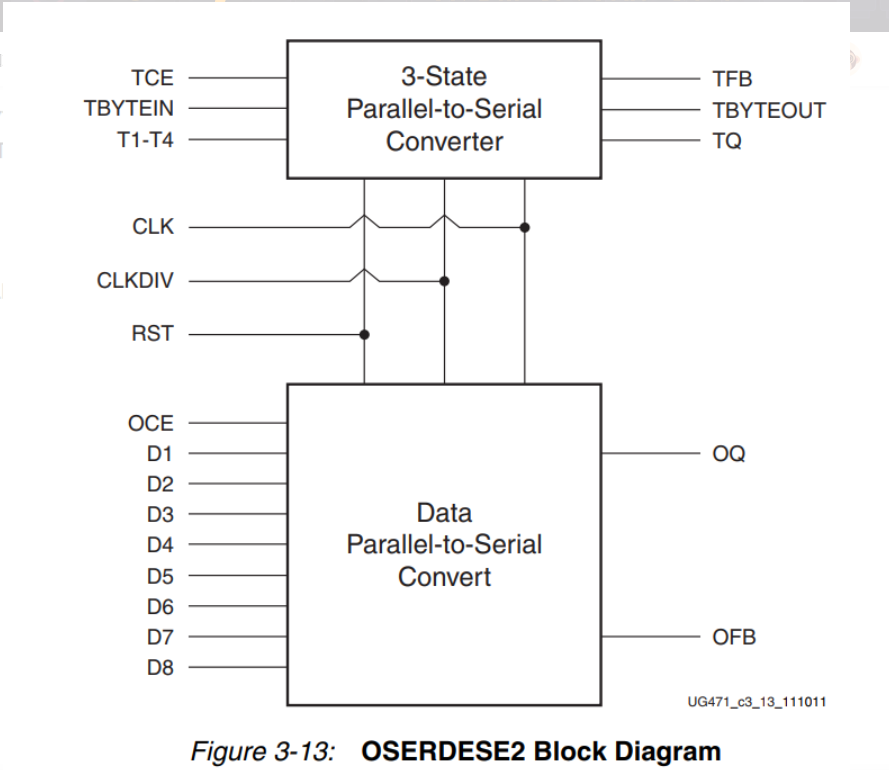

前言本文节选UG471的第三章,进行整理翻译,用于介绍高级SelectIO逻辑资源内部的OSERDESE2资源。输出并串逻辑资源 (OSERDESE2)简介7 系列器件中的 OSERDESE2 是专用的并串转换器,具有特定的时钟和逻辑资源,旨在促进高速源同步接口的实现。 每个 OSERDESE2 模...

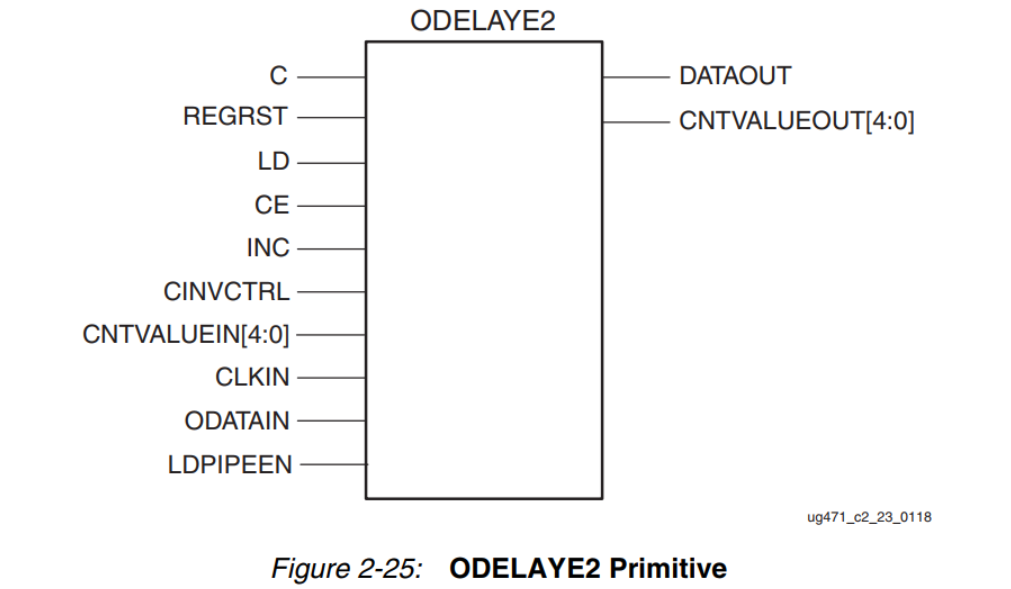

FPGA - 7系列 FPGA内部结构之SelectIO -06- 逻辑资源之ODELAY

前言本文节选UG471的第二章,进行整理翻译,用于介绍SelectIO资源内部的ODELAY资源。ODELAY资源简介输出延迟资源 (ODELAY) 在HR Bank 中不可用。每个 HP I/O 模块都包含一个称为 ODELAYE2 的可编程绝对延迟原语。ODELAY 可以连接到 OLOGICE2...

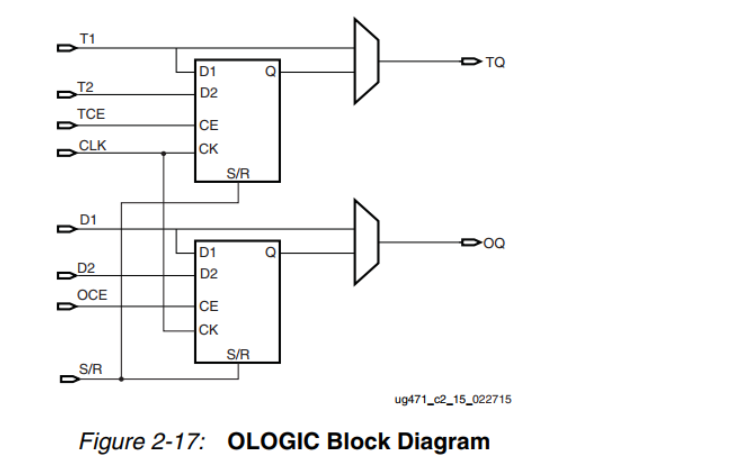

FPGA - 7系列 FPGA内部结构之SelectIO -05- 逻辑资源之OLOGIC

前言本文节选UG471的第二章,进行整理翻译,用于介绍SelectIO资源内部的OLOGIC资源。OLOGIC 资源简介OLOGIC 块位于 I/O 块 (IOB) 旁边。 OLOGIC 是一个专用的同步块,通过 IOB 从 FPGA 发送数据。 OLOGIC 资源的类型是 OLOGICE2(HP ...

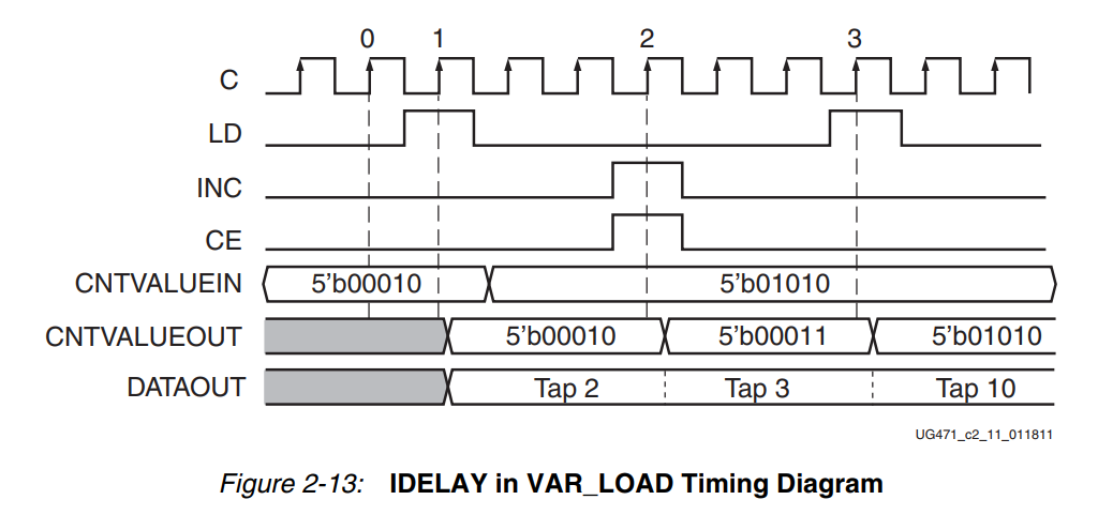

FPGA - 7系列 FPGA内部结构之SelectIO -04- 逻辑资源之IDELAY和IDELAYCTRL(二)

VAR_LOAD 模式下图显示了 VAR_LOAD 模式下的 IDELAY 时序图。时钟事件 0在 LD 产生脉冲之前,抽头设置和因此 CNTVALUEOUT 处于未知值。时钟事件 1在 C 的上升沿,LD 被检测为高电平,导致输出 DATAOUT 具有由 CNTINVALUE 定义的延迟,并将抽头...

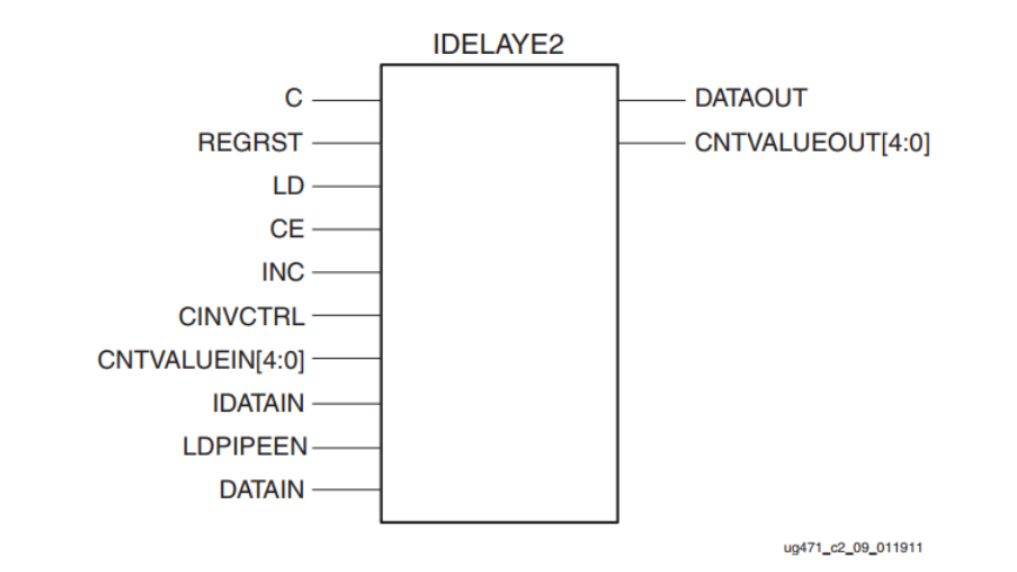

FPGA - 7系列 FPGA内部结构之SelectIO -04- 逻辑资源之IDELAY和IDELAYCTRL(一)

前言本文节选UG471的第二章,进行整理翻译,用于介绍SelectIO资源内部的IDELAY资源和IDELAYCTRL资源。输入延迟资源 (IDELAY)简介每个 I/O 模块都包含一个称为 IDELAYE2 的可编程延迟原语。 IDELAY 可以连接到 ILOGICE2/ISERDESE2 或 I...

FPGA - 7系列 FPGA内部结构之SelectIO -03- 逻辑资源之ILOGIC

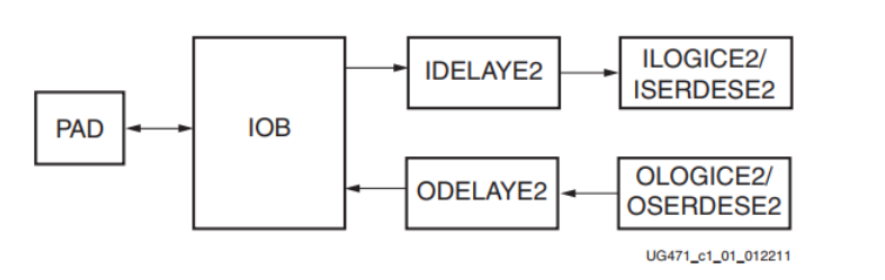

前言本文主要翻译节选自UG471,主要对7系列FPGA SelectIO逻辑资源进行简要介绍,然后介绍了内部的SelectIO逻辑资源的ILOGIC 资源。SelectIO逻辑资源简介7 系列 FPGA 包含来自之前系列的 Xilinx FPGA 的基本 I/O 逻辑资源。 这些资源包括:Combi...

FPGA - 7系列 FPGA内部结构之SelectIO -02- 源语简介(二)

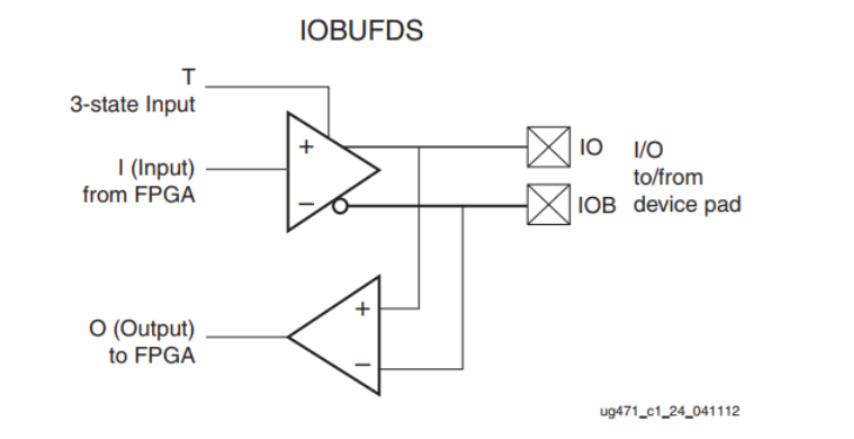

IOBUFDS下图显示了差分输入/输出缓冲器原语。 T引脚上的逻辑高电平禁用输出缓冲器。IOBUFDS_DCIEN下图所示的 IOBUFDS_DCIEN 原语在 HP I/O bank 中可用。 它有一个 IBUFDISABLE 端口,可用于在不使用缓冲区期间禁用输入缓冲区。 IOBUFDS_DCI...

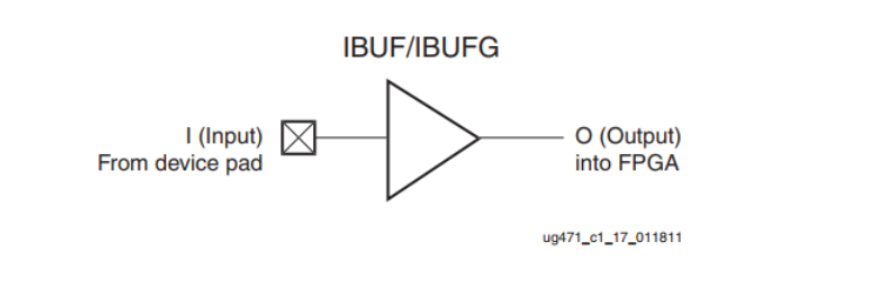

FPGA - 7系列 FPGA内部结构之SelectIO -02- 源语简介(一)

写在前面攻其事必先利其器,本文主要翻译节选自UG471,主要对7系列的xilinx FPGA IO资源的buffer源语进行简要说明,了解buffer的基本结构。7 系列 FPGA SelectIO原语Xilinx 软件库包含大量原语,以支持 7 系列 FPGA I/O 原语中可用的各种 I/O 标...

本页面内关键词为智能算法引擎基于机器学习所生成,如有任何问题,可在页面下方点击"联系我们"与我们沟通。

产品推荐

社区圈子