DP读书:鲲鹏处理器 架构与编程(四)内存顺序模型与内存屏障

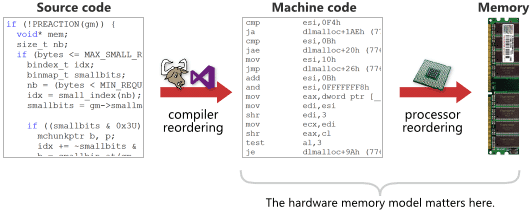

一、 访存重排序 在并行多核系统中,访问顺序不一定一致。为提升性能,编译器或硬件往往会对指令序列进行 重排序(Recording) ,从而引入乱序排序(Out-of-Order Execution) 机制 1. 指令重排序三种类型 编译器优化导致的指令序列重排序。不改变程序语义的情况下,对指令重新安...

鲲鹏开发重点-–扭转x86乾坤的挑战,ARM64内存模型

一、前言:扭转x86乾坤的挑战1、ARM:超越x86二选一思维2、Apple:推出惊人速度的ARM笔记本电脑3、鲲鹏:扭转x86乾坤的挑战二、指令乱序执行:独特架构的先进特性 1、体系结构决定内存模型:X86强内存序,ARM64是弱内存序2、X86强内存序: 写后读乱,读后读/写后写/读后写不乱3、...

本页面内关键词为智能算法引擎基于机器学习所生成,如有任何问题,可在页面下方点击"联系我们"与我们沟通。

产品推荐

最佳实践