内存系列学习(七):ARM处理器的快速上下文切换技术

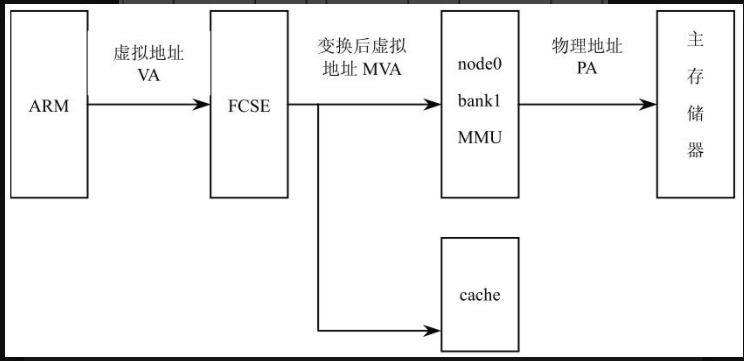

1 FCSE概述FCSE(Fast Context Switch Extension,快速上下文切换)位于CPU和MMU之间,如果两个进程使用了同样的虚拟地址空间,则对CPU而言,两个进程使用了同样的虚拟地址空间。**快速上下文切换机构对各进程的虚拟地址进行变换,**这样系统中除了CPU之外的部分看...

内存系列学习(五):ARM处理器中的Cache和Write Buffer

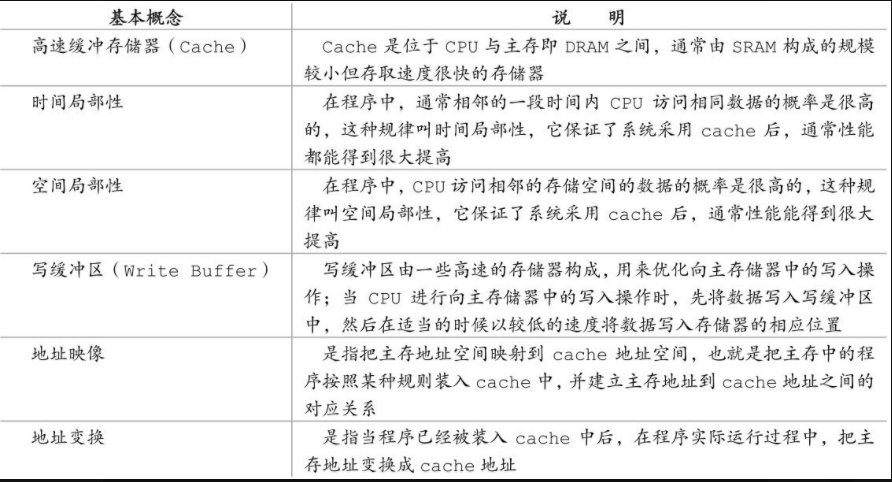

1 基本概念2 Cache工作原理在cache存储系统中,把cache和主存储器都划分成相同大小的块。主存地址由块号B和块内地址W两部分组成,cache地址由块号b和块内地址w组成。当CPU访问cache时,CPU送来主存地址,放到主存地址寄存器中,通过地址变换部件把主存地址中的块号B变换成cach...

内存系列学习(三):ARM处理器地址变换过程

一、MMU简介MMU是Memory Manage Unit的缩写,即存储管理单元的意思。MMU实现以下功能:1)虚拟存储地址到物理存储地址的映射;2)控制存储空间访问权限;3)设置存储空间的缓冲特性。与MMU相关的一些基本概念介绍如下:1-页表(Translate Table)页表又叫翻译表,用来将...

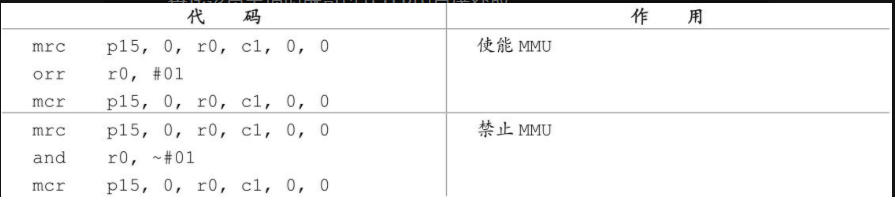

内存系列学习(二):ARM处理器中CP15协处理器

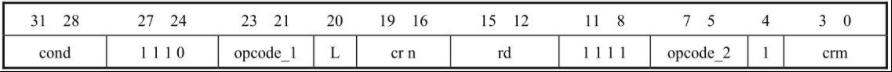

ARM处理器中CP15协处理器的寄存器0 前言之前我们在学习MMU的时候,知道这个内存的分配和CP15协处理器。这里先介绍一下CP15寄存器以及访问CP15寄存器的汇编指令。1 访问CP15寄存器的指令访问CP15寄存器指令的编码格式及语法说明如下:说明:<opcode_1>:协处理器行...

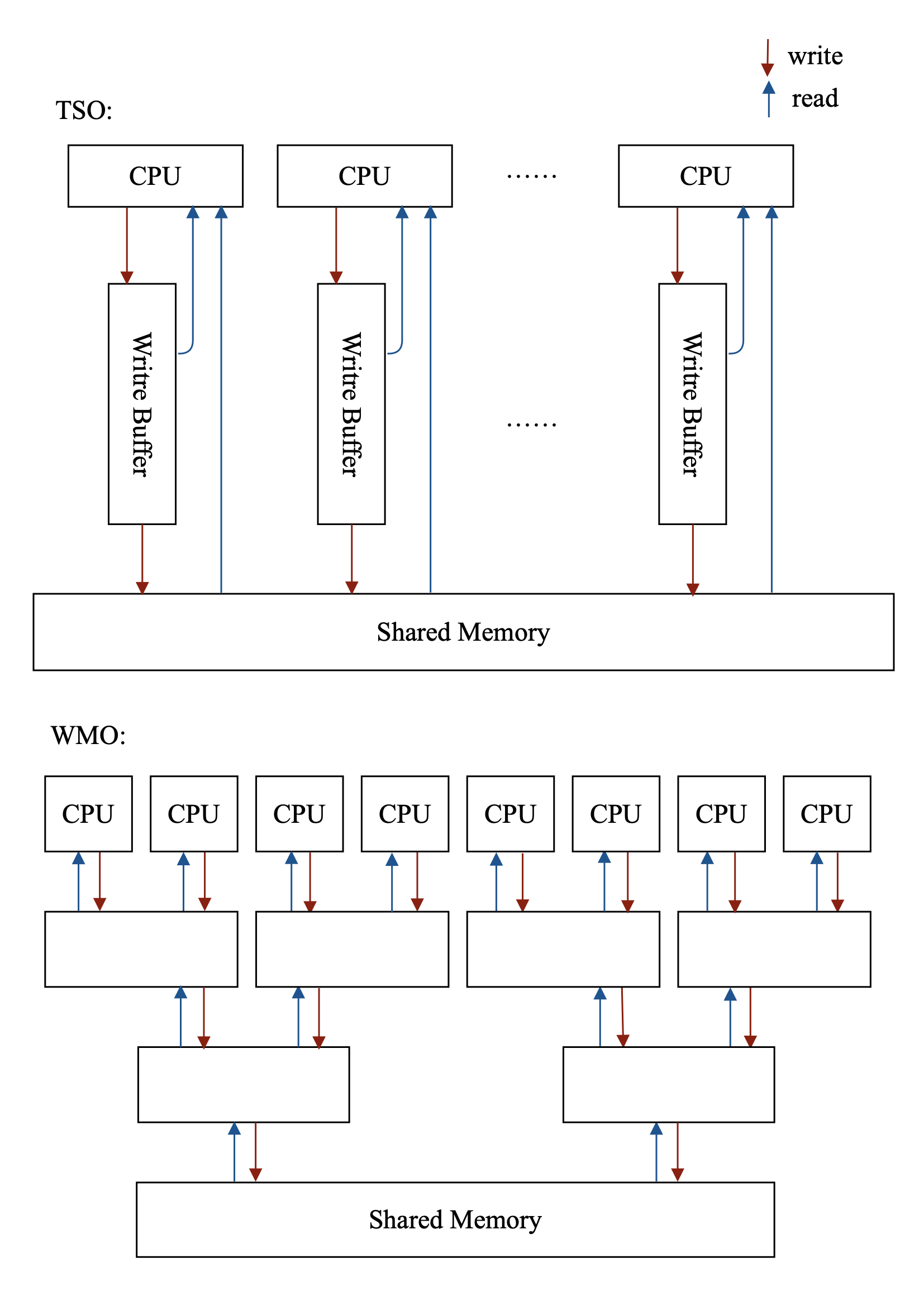

Hawkeyes: x86软件迁移Arm的弱内存序问题解决方案

背景介绍将多核多线程程序从x86架构的CPU迁移到Arm架构的CPU上往往会面临弱内存序问题。这个问题是迁移过程中的重大阻碍,也是很多业务方斟酌是否应该迁移到Arm机器上的一个关注焦点。因此如何正确且高效地解决这个问题意义重大,关乎Arm和倚天的生态建设。有许多团队曾经遇到过此类问题,给业务稳定性带...

linux-3.2.36内核启动2-setup_arch中的内存初始化1(arm平台 分析高端内存和初始化memblock)【转】

转自:http://blog.csdn.net/tommy_wxie/article/details/17093307 上一篇微博留下了这几个函数,现在我们来分析它们 sanity_check_meminfo();...

HPE、IBM、ARM以及三星等一众厂商正在联手编织“内存架构”

除了英特尔与思科之外,各家厂商皆已开始合作开发存储级内存方案。 HPE、IBM、ARM以及三星等一众厂商正在联手编织“内存架构” 存储级内存互连结构需求已经相当迫切 目前多家供应商已经开始携手开发Gen-Z方案——一套可扩展高性能总线或互连架构,旨在对接计算机与内存。 这一Gen-Z联盟属于开放性非...

ARM指令寻址方式之: 内存访问指令寻址

4.2 内存访问指令寻址 根据内存访问指令的分类,内存访问指令的寻址方式可以分为以下几种。 ① 字及无符号字节的Load/Store指令的寻址方式。 ② 杂类Load/Store指令的寻址方式。 ③ 批量Load/Store指令的寻址方式。 ④ 协处理器Load/Store指令的寻址方式...

Linux内核高-低端内存设置代码跟踪(ARM构架)

对于ARM中内核如何在启动的时候设置高低端内存的分界线(也是逻辑地址与虚拟地址分界线(虚拟地址)减去那个固定的偏移),这里我稍微引导下(内核分析使用Linux-3.0): 首先定位设置内核虚拟地址起始位置(也就是内核逻辑地址末端+1的地址)的文件:...

本页面内关键词为智能算法引擎基于机器学习所生成,如有任何问题,可在页面下方点击"联系我们"与我们沟通。

产品推荐

最佳实践