【芯片前端】根据数据有效选择输出的握手型FIFO结构探究

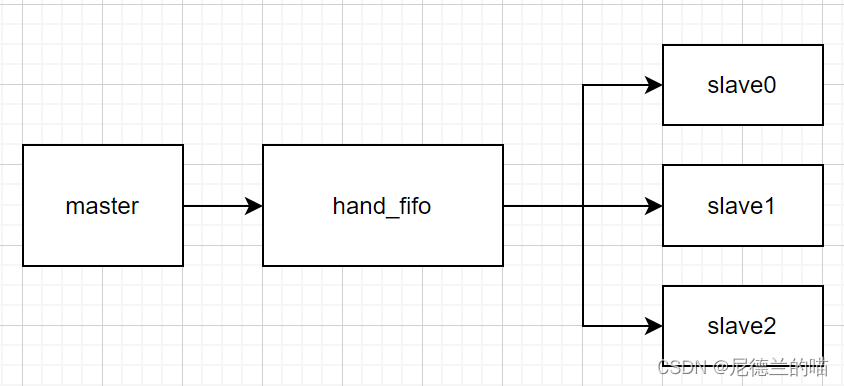

前言之前要做一个一读多写的fifo,也就是master写入数据到fifo中,多个slave读取数据,结构如下图所示:由于slave需要的数据一致,fifo内只需要例化一个ram以节约空间。这个fifo的具体结构下次博客中再来讨论。在这个fifo之后,又衍生出一个新的需求,就是master写入的数据并...

【芯片前端】延迟一拍出数的握手型ram结构的一次探索

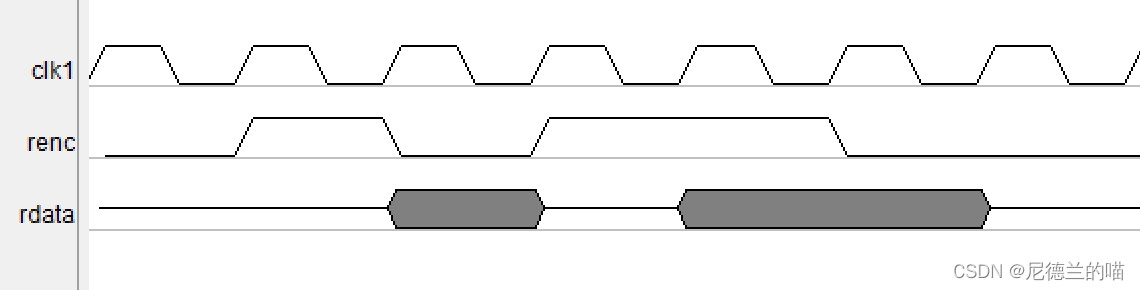

思路和代码并不一定正确,仅仅是记录一次有意思的结构思考过程,如有疏漏错误,请不吝赐教。一般而言生成的ram都是通过wenc/renc信号来控制读写,并且读使能后一拍读数据返回,当然,当ram深度较大时可能会延时。这次根据实际场景,ram本身是双口的一拍读取RAM。用下面的代码来代替ram内部的代码&...

【芯片前端】保持代码手感——一对多的握手拆分模块

前言最近还是在写spec文档,一天不写代码保持手感的大业就不能停止。这篇是握手拆分的模块,一般来说握手拆分有两种情况,一种是所有下游ready同时拉起了才向上握手,另外一种是下游可以分先后接收数据,每一路都接收完成后向上握手。本篇文章实现的是第二种形式。欢迎下载测试:verilog_cbb: 个人常...

【芯片前端】关于set_input_delay/set_output_delay慢信号约束到快时钟的思考

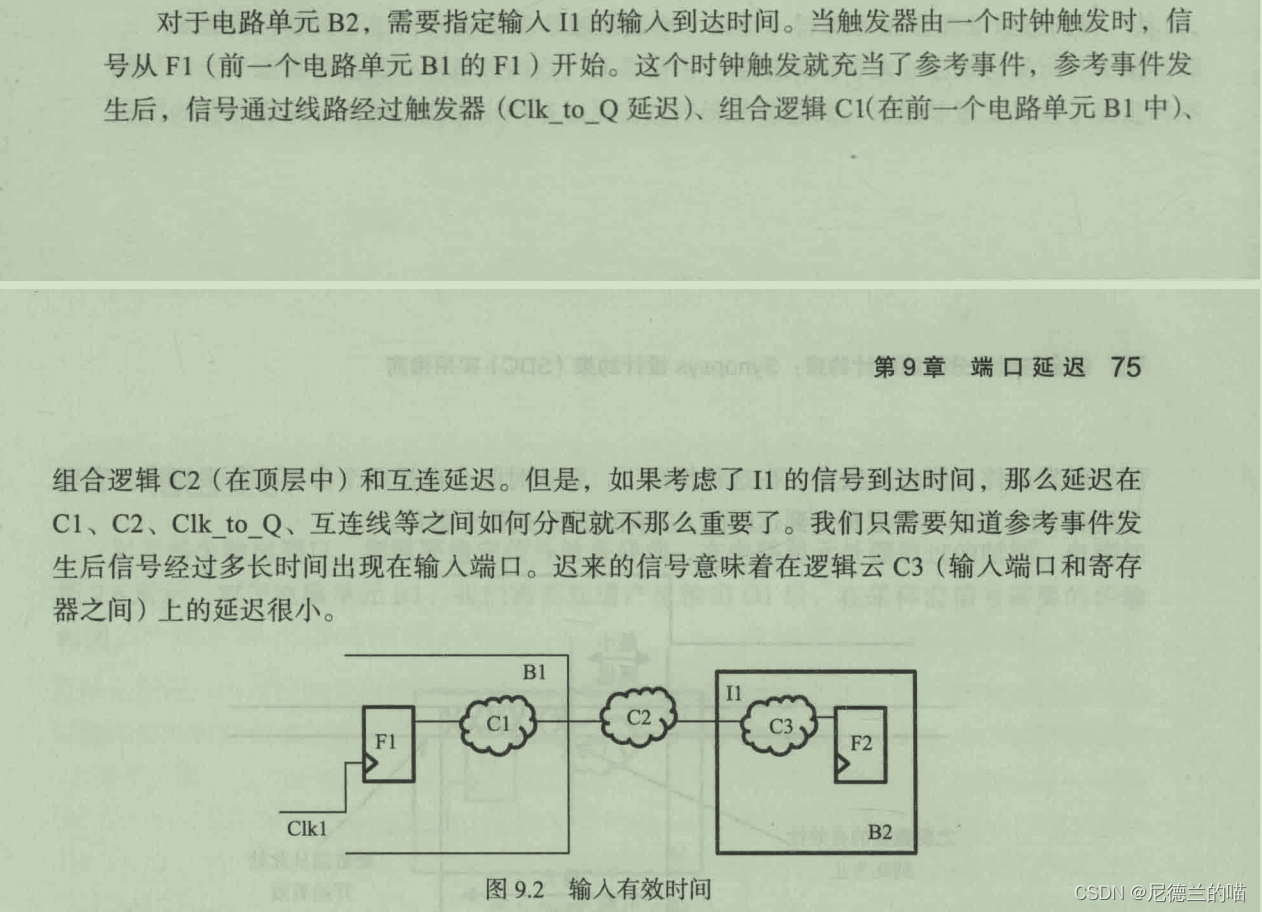

前言继续学习sdc的配置知识,这次思考的缘由是在写上一篇 【芯片前端】sdc学习日常——端口delay的正向设置与反向设置 中,写了这样一句话“还有一种方式,是把约束更恶劣的设置放在下面写,这样即使sigx被约束了两次,也会按更恶劣的配置进去。我理解更恶劣的应该是慢时钟的设置”。但事实上写这句话时...

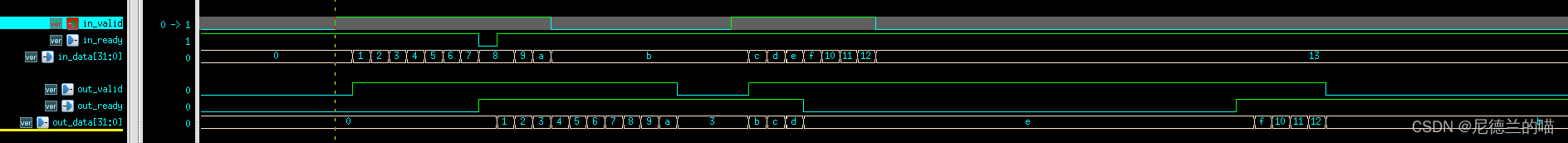

【芯片前端】保持代码手感——握手型同步fifo的进一步拓展

前言最近也是沉迷于握手协议的研究,主要是用的太多了要是不自己写写用起来就很没底。握手FIFO在 【芯片前端】保持代码手感——握手型同步FIFO设计 里,在设计时候有一个feature就是“对外输出逻辑时序较优”,因此对外的输出(除了data)都是寄存器输出,这客观上就是断开了输入和输出握手。在之前的...

【芯片前端】保持代码手感——握手型同步FIFO设计

前言工作中做了太久方案,还是要继续对代码手感的保持,这次完成握手型同步FIFO的RTL设计,设计规格如下:写入与读出均采用握手型接口;支持2的整数次与非整数次深度;对外输出逻辑时序较优;RTL设计对外接口握手型同步FIFO,接口如下:module sync_fifo #(...

【芯片前端】“异步FIFO全解析”的BUG——格雷码连续性

前言在前几天写完【芯片前端】保持代码手感——异步FIFO全解析之后自我感觉非常良好,觉得异步fifo的问题我已经全部拿捏了,没想到今天突然想到一个我自己代码里的bug。代码中的BUG事情的源头在同步fifo里,深度任意可配的同步fifo里使用了两个非饱和的cnt计数器记录读写地址指针,waddr和r...

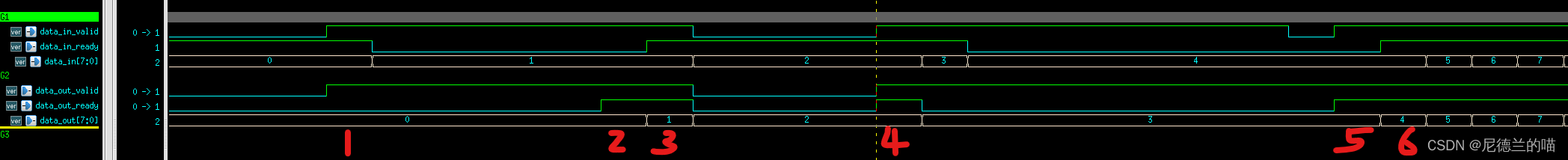

【芯片前端】保持代码手感——握手协议ready打拍时序优化

在valid-ready双向握手机制下,对下游反馈的ready进行打拍,实现对上游接口的ready信号时序优化。当拍若ready有效则数据可以直接向下游握手,若ready无效则数据寄存一拍。要求数据输出不能丢弃或乱序,且上游的ready为寄存器输出接口如下:module backward_pipe ...

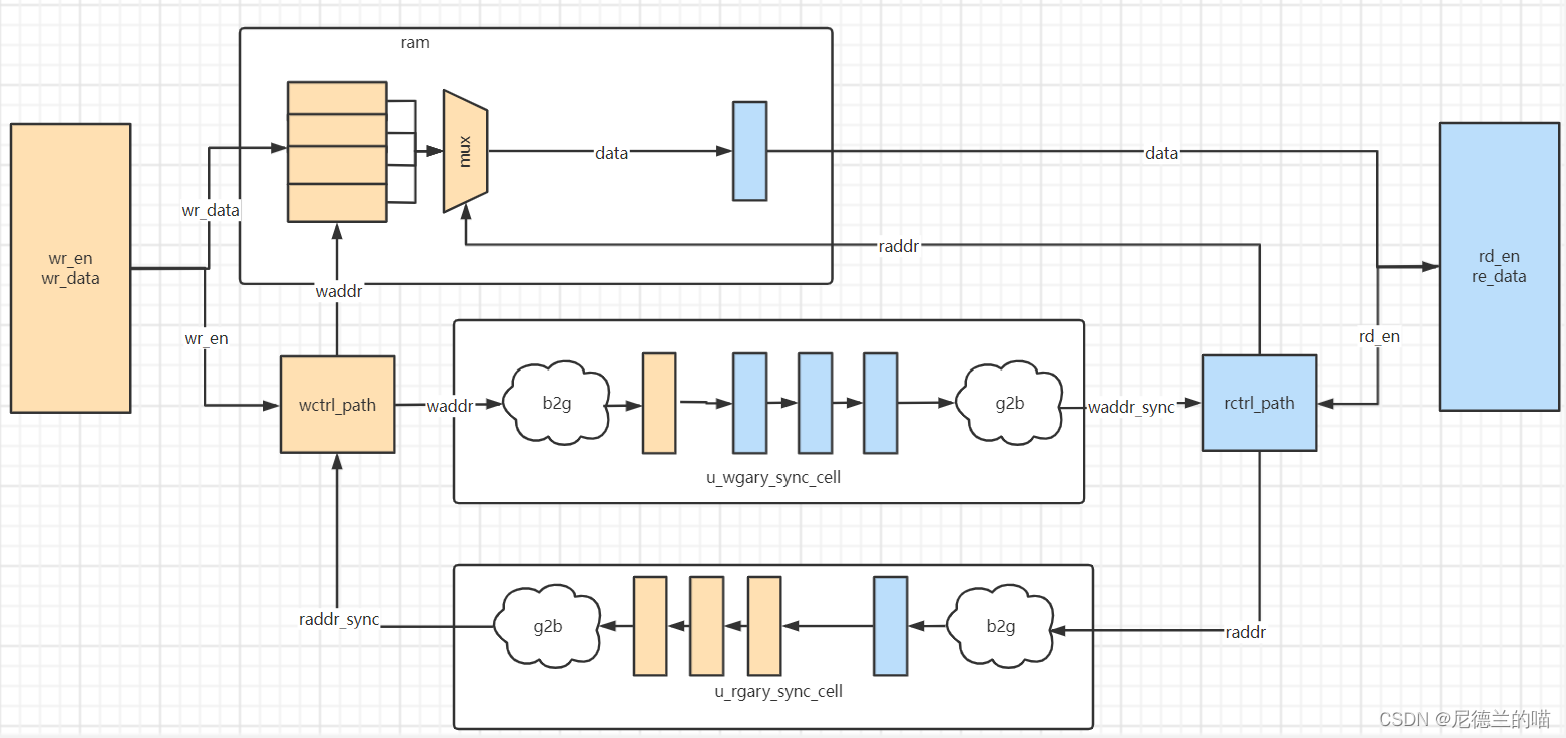

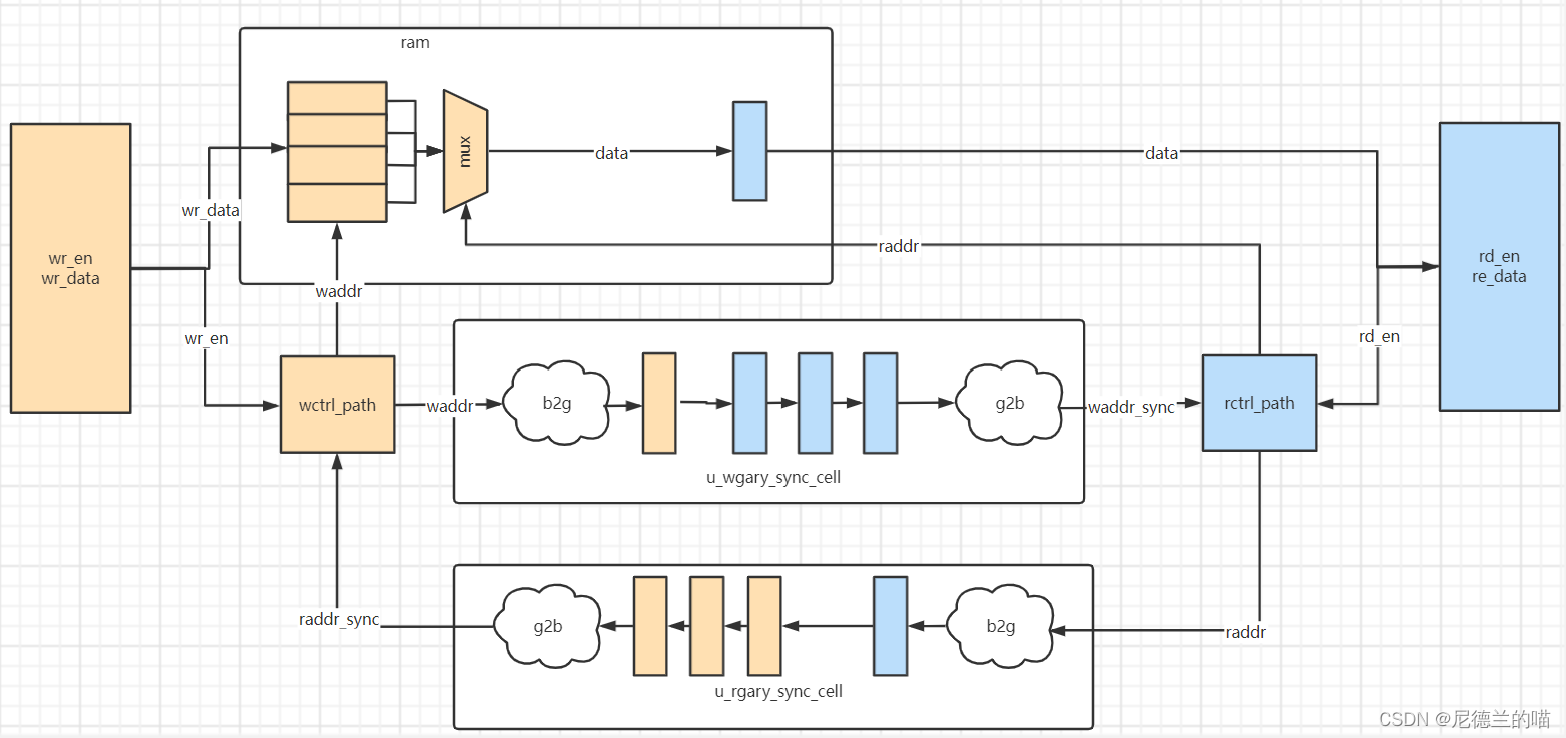

【芯片前端】保持代码手感——异步FIFO全解析

前言关于FIFO和异步处理我已经写过很多东西了:进阶之路——二进制与格雷码的相互转换模块设计【异步FIFO的一些小事·0】异步FIFO同步化设计【异步FIFO的一些小事·1】空满判断与格雷码【异步FIFO的一些小事·2】异步FIFO中异步走线延时约束的一些思考【异步FIFO的一些小事·3】异步FIF...

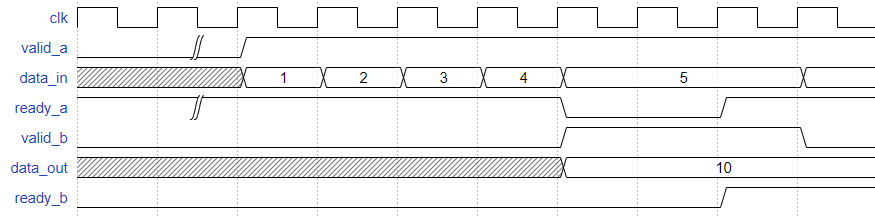

【芯片前端】保持代码手感——数据累加输出

实现串行输入数据累加输出,输入端输入8bit数据,每当模块接收到4个输入数据后,输出端输出4个接收到数据的累加结果。输入端和输出端与上下游的交互采用valid-ready双向握手机制。要求上下游均能满速传输时,数据传输无气泡,不能由于本模块的设计原因产生额外的性能损失。电路的接口如下图所示。vali...

本页面内关键词为智能算法引擎基于机器学习所生成,如有任何问题,可在页面下方点击"联系我们"与我们沟通。