m基于FPGA的256QAM调制信号产生模块verilog实现,包含testbench

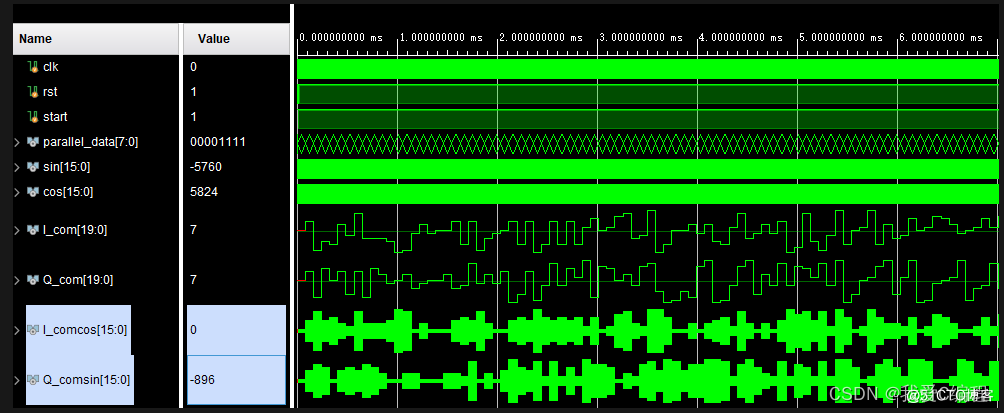

1.算法仿真效果 本系统进行Vivado2019.2平台的开发,其中Vivado2019.2仿真结果如下: 将基带导入到MATLAB显示星座图: 2.算法涉及理论知识概要 256QAM调制是一种高阶调制方式,具有较高的传输速率和频谱效率。在数字通信系统中,如何产生256QAM调制信号是一个重要的问题...

m基于FPGA的1024QAM调制信号产生模块verilog实现,包含testbench

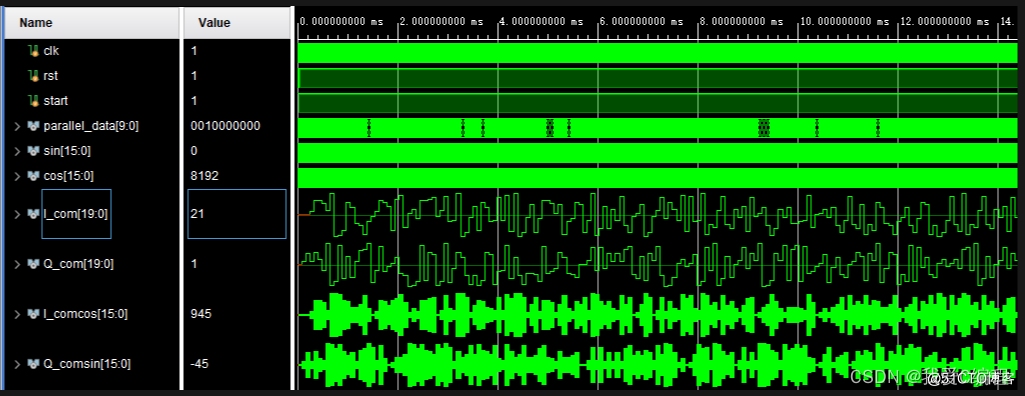

1.算法仿真效果 本系统进行了Vivado2019.2平台的开发,Vivado2019.2仿真结果如下: 将1024调制信号导入到matlab显示星座图 2.算法涉及理论知识概要 本文将详细介绍基于FPGA的1024QAM调制信号产生模块。本文将从以下几个方面进行介绍:1024QAM调制信号的基本原...

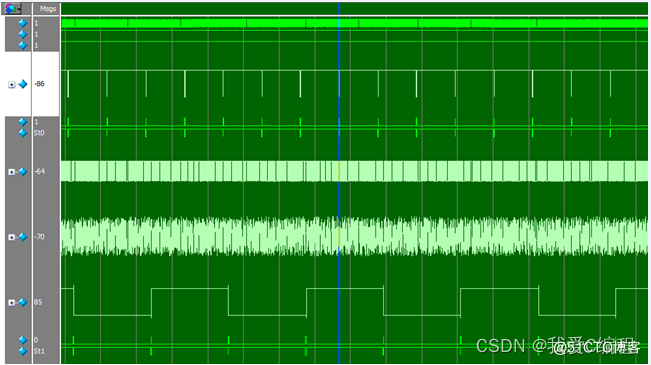

基于FPGA的直接序列扩频通信verilog设计,包括汉明编译码,扩频解扩,同步模块以及testbench

1.算法描述 与很多的通信技术类似,扩频技术最初也应用于保密通信和制导系统等军事技术。除了在军事通信中的应用,扩频技术在无线通信领域也有发展。目前扩频通信技术已经在测距、卫星通信、GPS导航定位、移动通信、电子对抗、跟踪、遥控和蓝牙技术等方面广泛应用。扩频通信技术具有很多独特的优点:具有抗干扰能力强...

m基于FPGA的NBDP系统ARQ单元模块的verilog实现

1.算法描述 NBDP(窄带直接印字电报),全称Narrow-Band Direct-Printing。是GMDSS地面无线民系统中的一种重要通信技术,这个终端设备,要与MF、HF设备联接使用。 什么是NBDP?解决这个问题先要了解一下什么是GMDSS GMDSS指Global Maritime D...

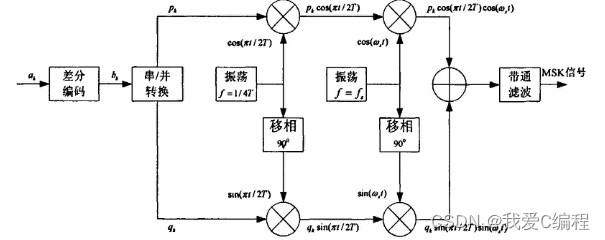

m基于FPGA的MSK调制解调系统verilog开发,并带FPGA误码检测模块和matlab仿真程序

1.算法描述整个模型的基本框图为软件无线电是现代通信技术的重要研究领域和发展方向,目前发展迅速.快速发展的软件无线电技术与落后的硬件计算资源之间的矛盾越来越突出.为了缓解这个矛盾,一方面可以加快集成电路的研发进度,提升硬件的计算性能;另一方面可以对信号处理的算法进行深入的改进研究,降低算法的运算量,...

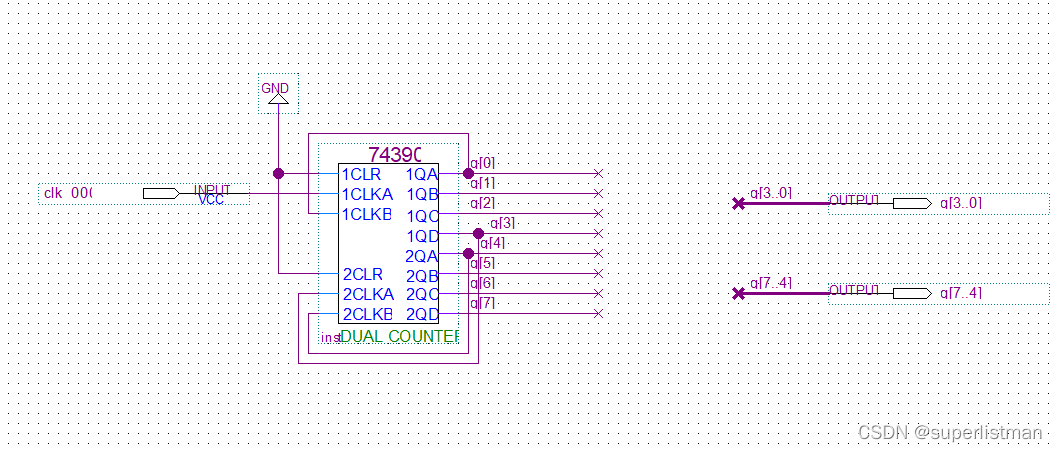

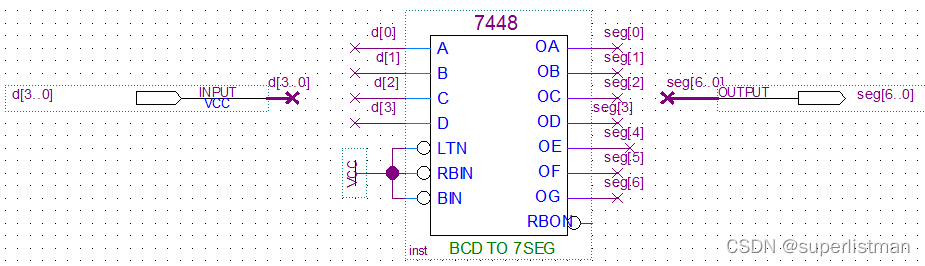

实验三 基于FPGA的数码管动态扫描电路设计 quartus/数码管/电路模块设计(下)

基本任务3:利用FPGA硬件平台上的6位数码管显示模100计数结果(以1S为节拍);1、电路设计(1)实验三就有一些复杂了。要实现模100计数结果,我们首先要有一个模100计数器。cnt100(2)第二个新模块是sec_select模块,之所以这么命名和设计...

实验三 基于FPGA的数码管动态扫描电路设计 quartus/数码管/电路模块设计(上)

实验三 基于FPGA的数码管动态扫描电路设计源文件的链接放在最后啦实验目的:(1) 熟悉7段数码管显示译码电路的设计。(2) 掌握数码管显示原理及静态、动态扫描电路的设计。实验任务:(1) 基本任务1:利用FPGA硬件平台上的4位数码管做静态显示,用SW0-...

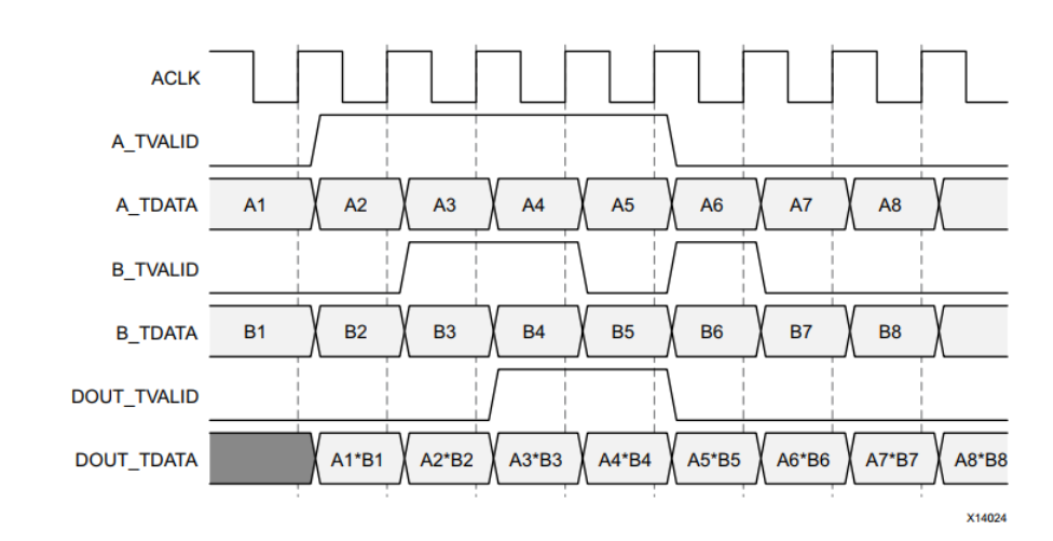

数字信号处理-05- FPGA常用运算模块-复数乘法器(二)

非阻塞模式非阻塞意味着如果在另一个输入通道上接收到数据,则一个输入通道上缺少数据不会阻止操作的执行。并非总是需要 AXI4-Stream 的完整流量控制。 使用 FlowControl 参数或 GUI 字段选择阻塞或非阻塞行为。 复乘法器支持 NonBlocking 模式,其中 AXI4-Strea...

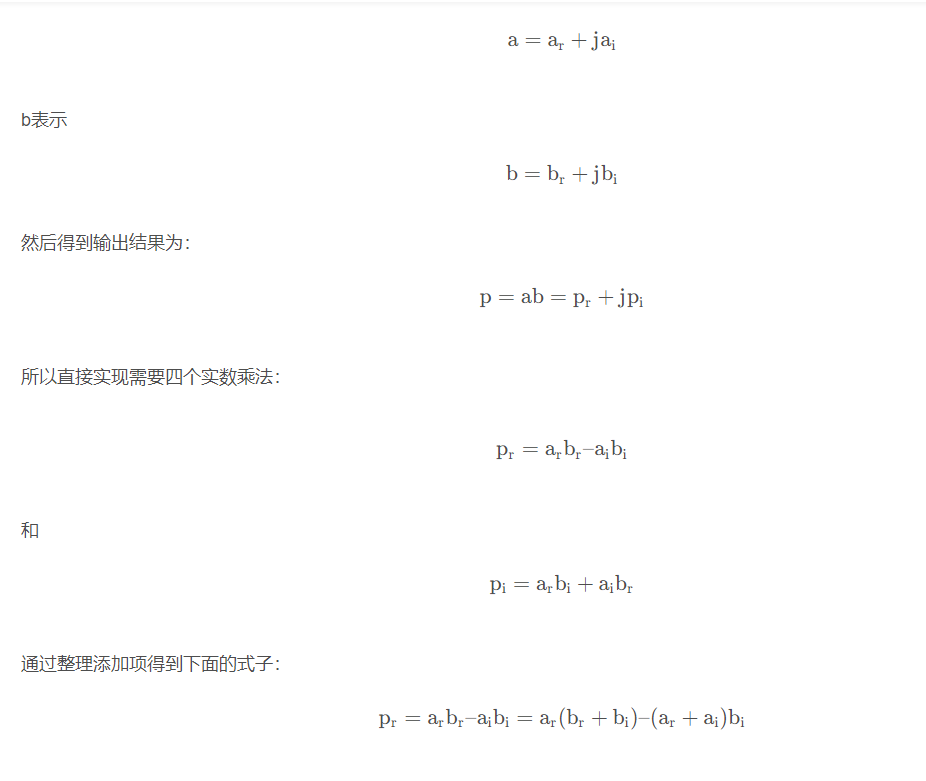

数字信号处理-05- FPGA常用运算模块-复数乘法器(一)

写在前面本文是本系列的第五篇,本文主要介绍FPGA常用运算模块-复数乘法器,xilinx提供了相关的IP以便于用户进行开发使用。复数乘法器复数乘法器IP基于用户指定的选项实现了符合 AXI4-Stream 的高性能、优化的复数乘法器。两个被乘数输入和可选的舍入位在独立的 AXI4-Stream 通道...

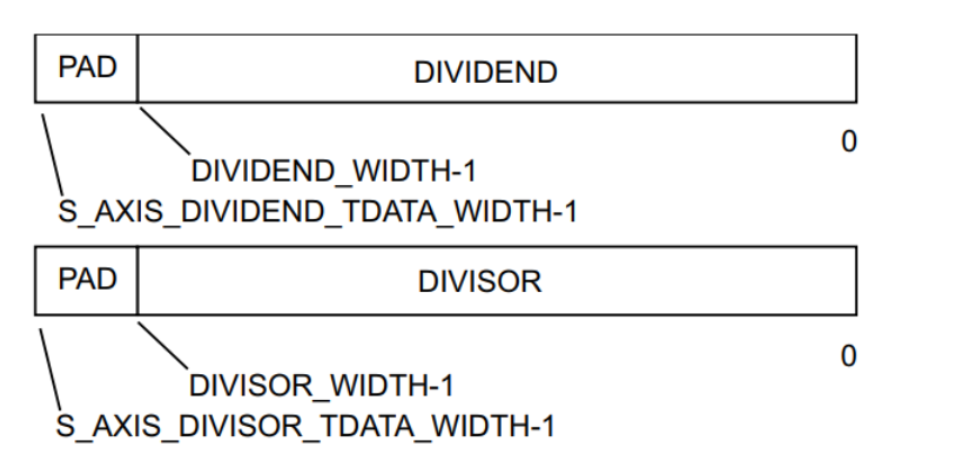

数字信号处理-04- FPGA常用运算模块-除法器(二)

TDATA包AXI4-Stream 接口中的遵循特定的命名法。 在该内核中,操作数通过通道 tdata 端口传入或传出内核。 为了简化协议的互操作性,如果需要时,首先扩展 tdata 中可以独立使用的每个子字段,以适应 8 位倍数的位字段。 对于输出 DOUT 通道,结果字段符号扩展到字节边界。 由...

本页面内关键词为智能算法引擎基于机器学习所生成,如有任何问题,可在页面下方点击"联系我们"与我们沟通。

产品推荐

社区圈子

FPGA云服务器更多模块相关

- FPGA云服务器verilog模块

- FPGA云服务器同步模块

- FPGA云服务器数码模块

- 数字信号处理FPGA云服务器运算模块乘法器

- 信号处理FPGA云服务器模块复数乘法

- 数字信号处理FPGA云服务器运算模块

- 数字信号处理FPGA云服务器运算模块除法器

- FPGA云服务器控制器模块

- 黑金FPGA云服务器驱动模块

- 黑金教程FPGA云服务器驱动实验模块

- FPGA云服务器驱动模块

- 教程FPGA云服务器驱动模块

- 黑金FPGA云服务器模块

- 黑金FPGA云服务器实验模块

- 教程FPGA云服务器驱动实验模块读写

- 黑金教程FPGA云服务器模块读写

- FPGA云服务器驱动实验模块读写

- 教程FPGA云服务器sdram模块读写

- FPGA云服务器实验tft模块

- 黑金FPGA云服务器模块双击

- FPGA云服务器串口模块

- FPGA云服务器实验sdram模块