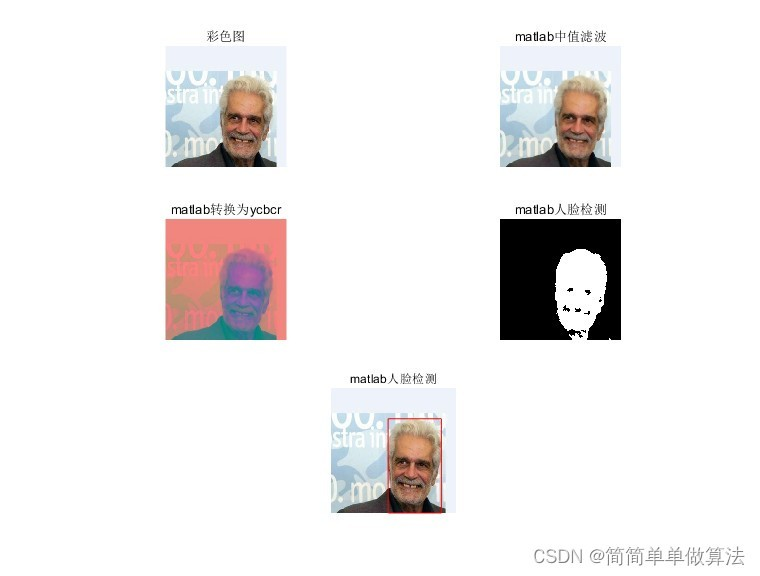

基于肤色模型的人脸识别FPGA实现,包含tb测试文件和MATLAB辅助验证

1.算法运行效果图预览matlab2022a的测试结果如下: vivado2019.2的仿真结果如下: 将数据导入到matlab中, 系统的RTL结构图如下图所示: 系统包括中值滤波,RGB转换为ycbcr,人脸检测三个模块 2.算法运行软件版本vivado2019.2 matlab2022a 3....

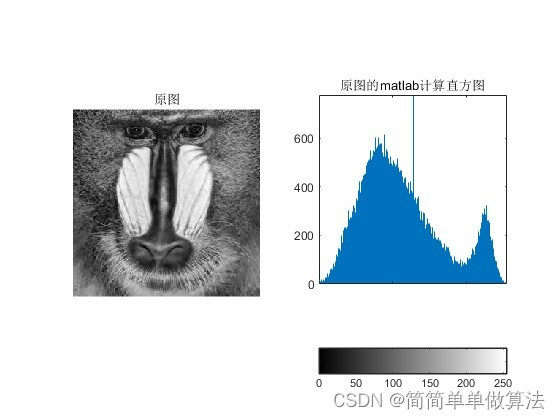

基于直方图的图像曝光量分析FPGA实现,包含tb测试文件和MATLAB辅助验证

1.算法运行效果图预览正常图像: checkb位于f192b和f250b之间 多度曝光图像: checkb位于f192b和f250b之外,判决为曝光过度。 2.算法运行软件版本vivado2019.2 matlab2022a 3.算法理论概述参考资料如下: 主要采用的方法为: 4.部分核心程序 ``...

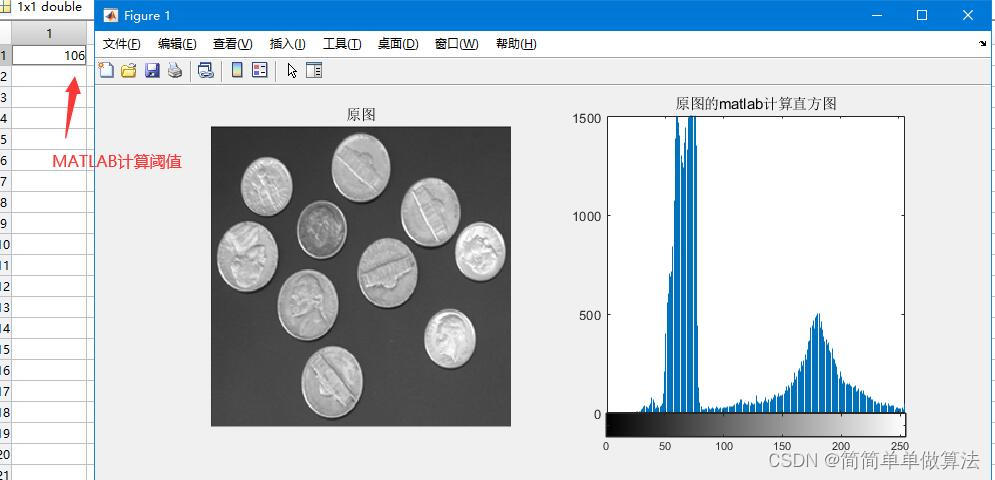

基于直方图的图像阈值计算和分割算法FPGA实现,包含tb测试文件和MATLAB辅助验证

1.算法运行效果图预览 2.算法运行软件版本VIVADO2019.2 matlab2022a 3.算法理论概述 图像阈值计算和分割是图像处理领域的一项重要任务,它通过设定一个阈值将图像从灰度空间转化为二值空间,从而实现对图像区域的有效划分。基于直方图的阈值选取方法主要依赖于图像的灰度直方图分布特性。...

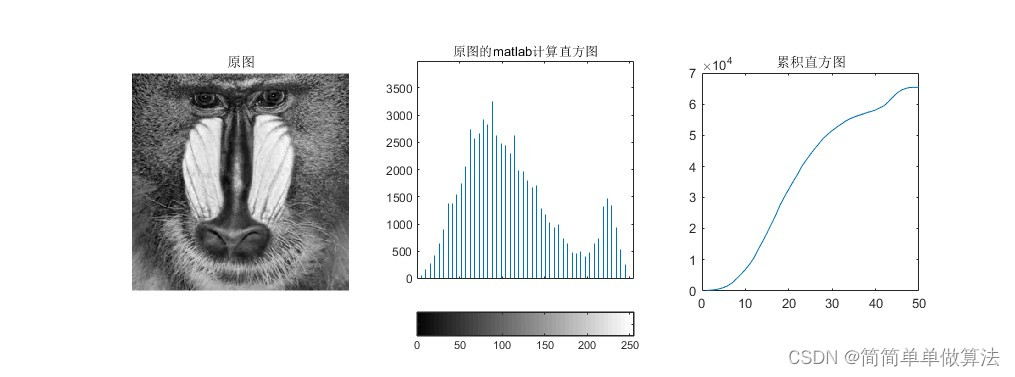

基于FPGA的图像累积直方图verilog实现,包含tb测试文件和MATLAB辅助验证

1.算法运行效果图预览 2.算法运行软件版本Vivado2019.2 matlab2022a 3.算法理论概述 图像累积直方图是一种重要的图像特征表示方法,它统计了图像中像素值累加分布的情况,广泛应用于图像增强、对比度调整、颜色校正、图像分割、目标检测等领域。FPGA作为一种高性能、低功耗的可重构硬...

m基于FPGA的多通道FIR滤波器verilog实现,包含testbench测试文件

1.算法仿真效果VIVADO2019.2仿真结果如下: 系统RTL结构如下: 2.算法涉及理论知识概要 多通道FIR(Finite Impulse Response)滤波器是一种在数字信号处理中广泛应用的线性时不变滤波技术,尤其适用于多通道音频、视频、图像等多维数据的处理。 单通道FIR滤波器可由其...

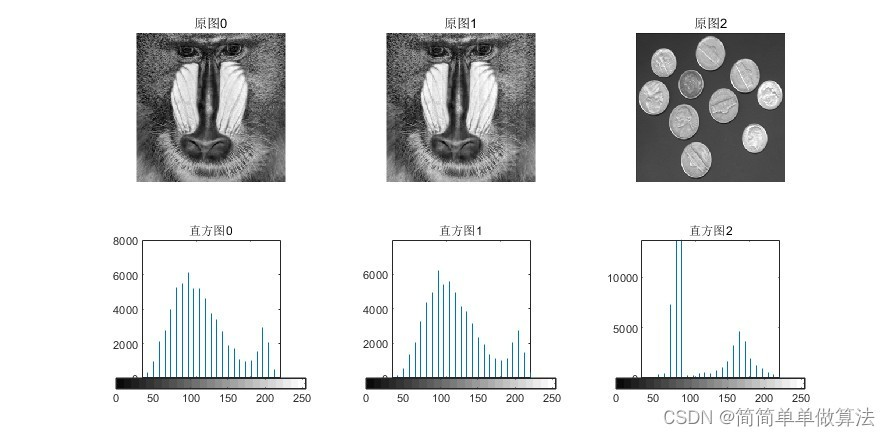

基于直方图相似性的图像分类算法FPGA实现,包括tb测试文件和MATLAB辅助验证

1.算法运行效果图预览MATLAB测试结果: FPGA测试结果: 上述仿真图中,红色XX表示图像读取完毕。因此输出XX。当图像输出完成之后,最下面的相似性指标 same1输出为11226,same2输出为67584.即图1和图2相似性较强,图1和图3相似性较弱。 2.算法运行软件版本vivado20...

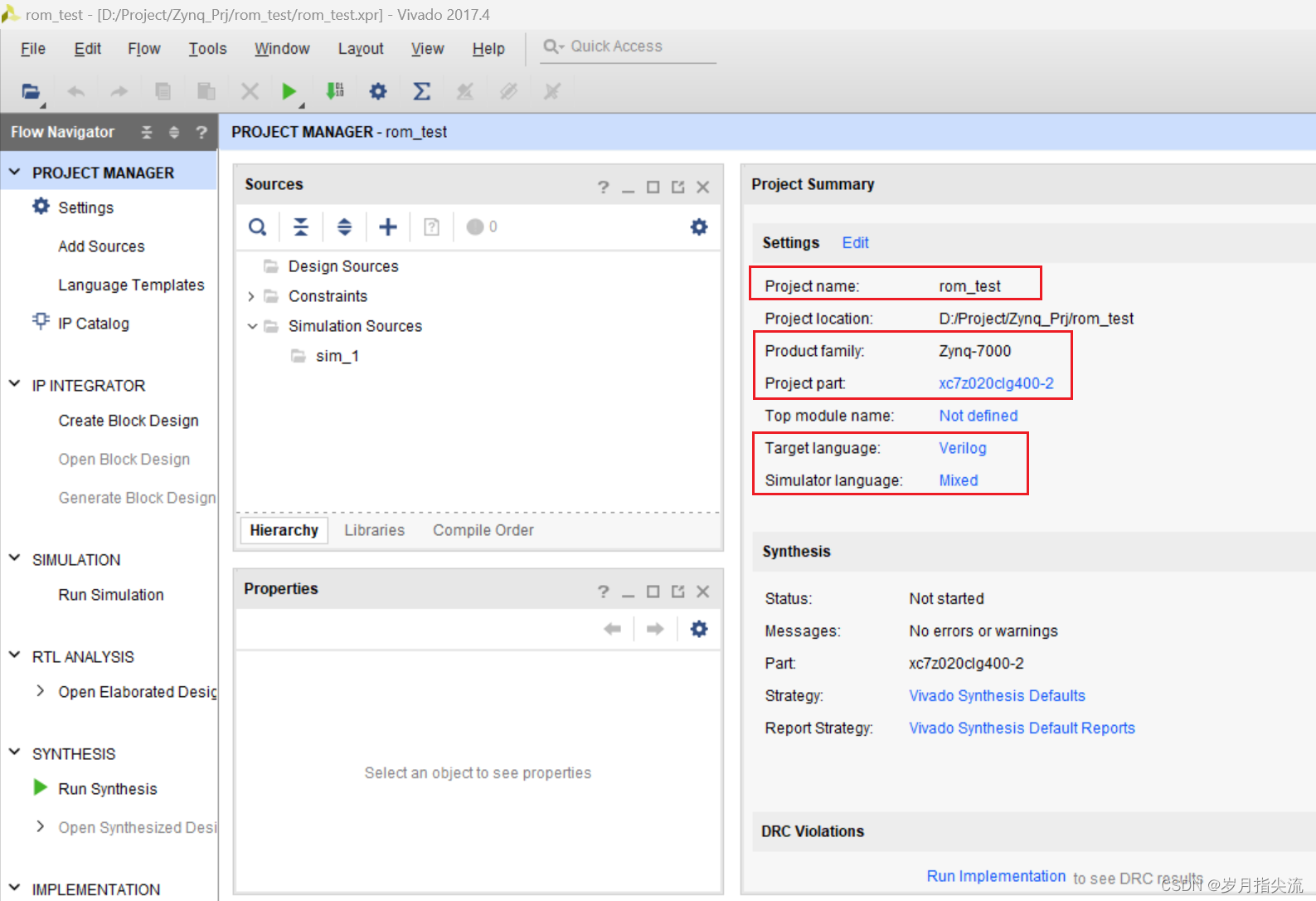

FPGA片内ROM测试实验(二)

FPGA片内ROM测试实验(一)https://developer.aliyun.com/article/1472299 三、程序编写 1、新建测试程序 新建 rom_test.v 源文件并将下面的程序块拷贝过去 rom_test.v `tim...

FPGA片内ROM测试实验(一)

前言 FPGA 本身是 SRAM 架构的,断电之后程序就会消失,那么如何利用 FPGA 实现一个 ROM 呢,我们可以利用 FPGA 内部的 RAM 资源实现 ROM,但这不是真正意义上的 ROM,而是每次上电都会把初始化的值先写入 RAM。Vivado 软件中提供了 ROM 的 IP 核 , 我们...

基于肤色模型和中值滤波的手部检测算法FPGA实现,包括tb测试文件和MATLAB辅助验证

1.算法运行效果图预览RTL图: 仿真图: 导入到matlab显示效果如下: 2.算法运行软件版本matlab2022a vivado2019.2 3.算法理论概述 在计算机视觉领域,基于肤色模型和中值滤波的手部检测方法是一种常见的初步定位策略。该方法主要分为两大部分:肤色分割以区分出图像中的皮肤区...

m基于FPGA的电子钟verilog实现,可设置闹钟,包含testbench测试文件

1.算法仿真效果本系统进行Vivado2019.2平台的开发,测试结果如下所示: 2.算法涉及理论知识概要 电子钟是现代生活中常见的计时工具,其准确性和功能性不断提高。基于FPGA的电子钟设计不仅具有灵活的可定制性,还能通过集成其他功能(如闹钟)来增强实用性。Verilog作为一种广泛使用的硬件描述...

本页面内关键词为智能算法引擎基于机器学习所生成,如有任何问题,可在页面下方点击"联系我们"与我们沟通。

产品推荐

社区圈子