m基于FPGA的RS+卷积级联编译码实现,RS用IP核实现,卷积用verilog实现,包含testbench测试文件

1.算法仿真效果Vivado2019.2仿真结果如下: 2.算法涉及理论知识概要 级联码是一种通过将两种或多种纠错码结合使用来提高纠错能力的编码方案。在RS+卷积级联编码中,通常首先使用卷积码对原始数据进行编码,以增加冗余并提供一定的纠错能力。然后,将卷积码的输出作为RS码的输入进行进一步编码,以增...

m基于FPGA和IP核的RS编译码verilog实现,包含testbench测试文件

1.算法仿真效果本系统进行了Vivado2019.2平台的开发,测试结果如下: 2.算法涉及理论知识概要 在现代通信系统中,为了确保数据传输的可靠性,经常需要使用各种纠错编码技术。其中,里德-所罗门(Reed-Solomon, RS)码是一种非常强大的线性纠错码,特别适用于纠正多个随机符号错误。随着...

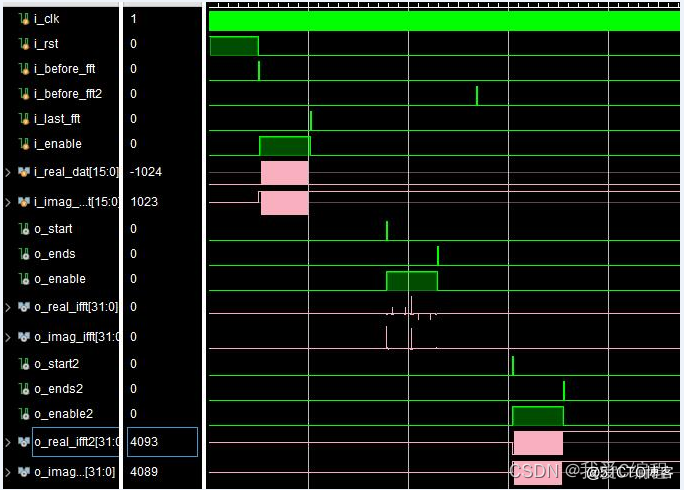

基于FPGA的FFT变换和反变换实现,使用IP核设计,包含testbench

1.算法仿真效果VIVADO2019.2仿真结果如下: 输入信号实部和虚部 FFT变换实部和虚部 IFFT变换实部和虚部恢复原始输入数据 2.算法涉及理论知识概要 快速傅里叶变换 (fast Fourier transform), 即利用计算机计算离散傅里叶变换(DFT)的高效、快速计算方法的统称,...

本页面内关键词为智能算法引擎基于机器学习所生成,如有任何问题,可在页面下方点击"联系我们"与我们沟通。

产品推荐

社区圈子

FPGA云服务器testbench相关内容

- FPGA云服务器testbench matlab

- FPGA云服务器testbench matlab程序

- FPGA云服务器testbench验证程序

- FPGA云服务器testbench程序

- FPGA云服务器fir testbench

- FPGA云服务器滤波器testbench文件

- FPGA云服务器testbench文件

- FPGA云服务器滤波器testbench

- FPGA云服务器译码testbench

- 算法FPGA云服务器testbench matlab

- 算法FPGA云服务器testbench

- FPGA云服务器变换逆变换testbench

- FPGA云服务器编译码testbench

- FPGA云服务器变换testbench

- FPGA云服务器计算testbench

- FPGA云服务器信号testbench

- FPGA云服务器滤波testbench

- FPGA云服务器testbench验证

- FPGA云服务器图像testbench

- FPGA云服务器汉明编译码testbench

- FPGA云服务器ofdm testbench

- FPGA云服务器开发testbench

- FPGA云服务器testbench测试程序

- cordic补偿FPGA云服务器包含testbench

- 基带FPGA云服务器包含testbench

- 导频基带FPGA云服务器包含testbench

- 基带信号FPGA云服务器testbench

- FPGA云服务器testbench配置

- FPGA云服务器testbench星座

- FPGA云服务器qam信号testbench

- FPGA云服务器相位testbench

- FPGA云服务器调制通信testbench

- FPGA云服务器系统testbench载波同步

- FPGA云服务器开发包含testbench

- FPGA云服务器控制器testbench

- 状态机方法FPGA云服务器testbench

- FPGA云服务器算法实现包含testbench

- FPGA云服务器testbench信号