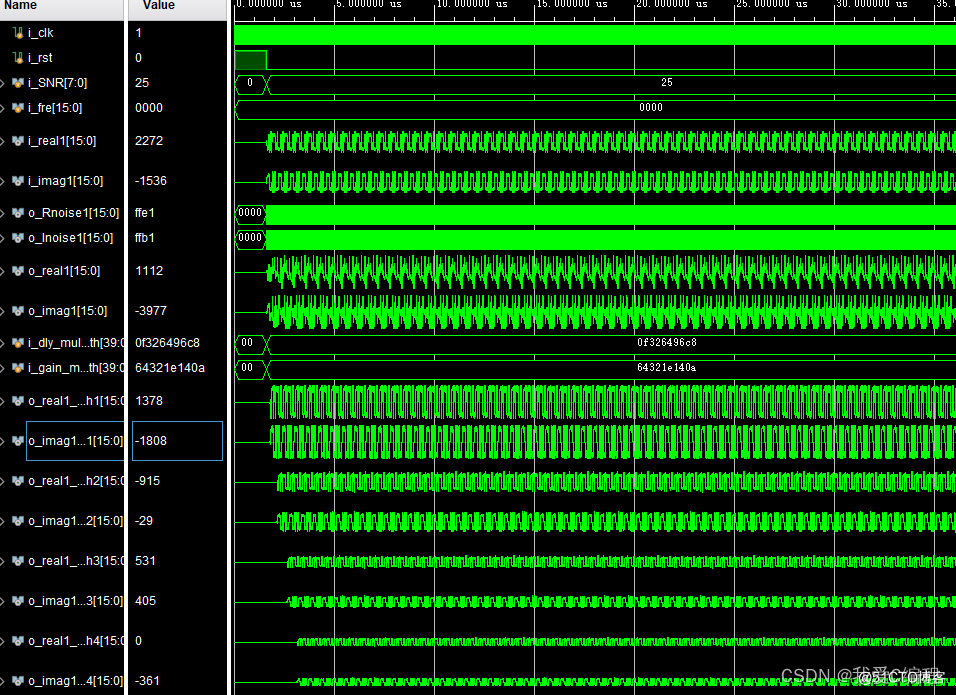

m基于FPGA的多径信道模拟verilog实现,包含testbench,可配置SNR,频偏,多径增益和多径延迟

1.算法仿真效果其中Vivado2019.2仿真结果如下: 2.算法涉及理论知识概要 瑞利分布是一个均值为0,方差为σ²的平稳窄带高斯过程,其包络的一维分布是瑞利分布。其表达式及概率密度如图所示。瑞利分布是最常见的用于描述平坦衰落信号接收包络或独立多径分量接受包络统计时变特性的一种分布类型。两个正交...

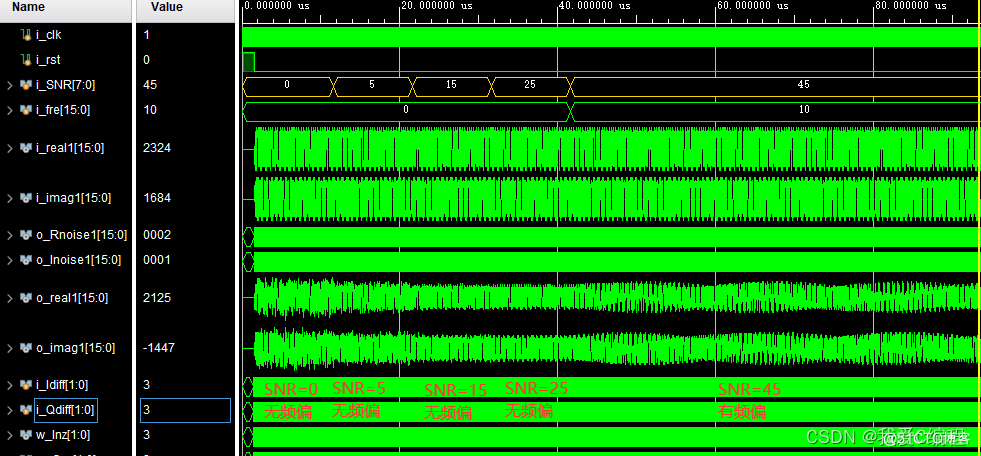

m基于FPGA的高斯白噪声信道模拟系统verilog实现,包含testbench,可以配置不同的SNR和频偏

1.算法仿真效果vivado2019.2仿真结果如下: SNR=0db,无频偏 SNR=5db,无频偏 SNR=25db,无频偏 SNR=45db,带频偏 2.算法涉及理论知识概要 高斯白噪声信道在通信系统中具有重要意义,模拟此类信道有助于评估系统性能。本文提出的FPGA实现系统可以灵活地模拟不同信...

m基于FPGA的数据串并并串转换系统verilog实现,包含testbench,可以配置并行数量

1.算法仿真效果 本系统进行了两个平台的开发,分别是: Vivado2019.2 Quartusii18.0+ModelSim-Altera 6.6d Starter Edition 其中Vivado2019.2仿真结果如下: 分别进行2路,4路,8路,16路并行串行转换 Quartusii18.0...

本页面内关键词为智能算法引擎基于机器学习所生成,如有任何问题,可在页面下方点击"联系我们"与我们沟通。

产品推荐

社区圈子

FPGA云服务器testbench相关内容

- FPGA云服务器testbench matlab

- FPGA云服务器testbench matlab程序

- FPGA云服务器testbench验证程序

- FPGA云服务器testbench程序

- FPGA云服务器fir testbench

- FPGA云服务器滤波器testbench文件

- FPGA云服务器testbench文件

- FPGA云服务器滤波器testbench

- FPGA云服务器译码testbench

- 算法FPGA云服务器testbench matlab

- 算法FPGA云服务器testbench

- FPGA云服务器变换逆变换testbench

- FPGA云服务器ip testbench

- FPGA云服务器编译码testbench

- FPGA云服务器变换testbench

- FPGA云服务器计算testbench

- FPGA云服务器信号testbench

- FPGA云服务器滤波testbench

- FPGA云服务器testbench验证

- FPGA云服务器图像testbench

- FPGA云服务器汉明编译码testbench

- FPGA云服务器ofdm testbench

- FPGA云服务器开发testbench

- FPGA云服务器testbench测试程序

- cordic补偿FPGA云服务器包含testbench

- 基带FPGA云服务器包含testbench

- 导频基带FPGA云服务器包含testbench

- 基带信号FPGA云服务器testbench

- FPGA云服务器testbench星座

- FPGA云服务器qam信号testbench

- FPGA云服务器相位testbench

- FPGA云服务器调制通信testbench

- FPGA云服务器系统testbench载波同步

- FPGA云服务器开发包含testbench

- FPGA云服务器控制器testbench

- 状态机方法FPGA云服务器testbench

- FPGA云服务器算法实现包含testbench

- FPGA云服务器testbench信号