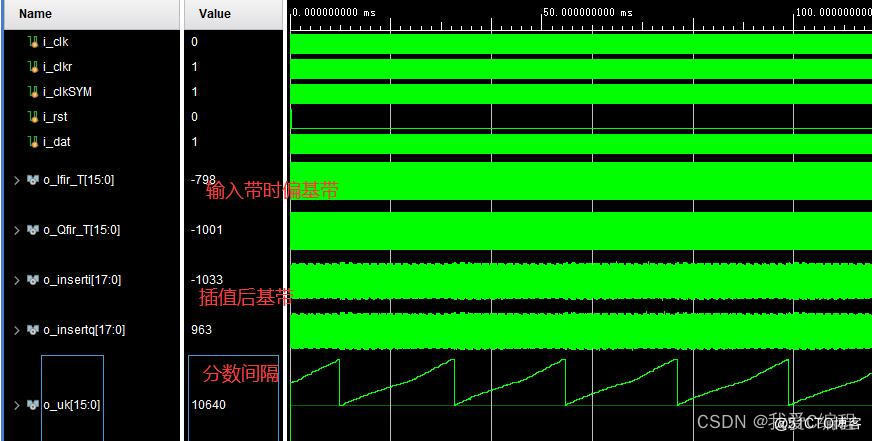

m基于FPGA的gardner环定时同步实现,含testbench测试程序

1.算法仿真效果使用vivaod2019.2版本仿真结果如下: 将基带信号放大可以看到: 整个系统的RTL图如下图所示: 其中gardner环的结构如下图所示: 2.算法涉及理论知识概要 基于FPGA的Gardner环定时同步是一种用于数字通信系统中实现定时同步的高效方法。该方法通过提取接收信号中的...

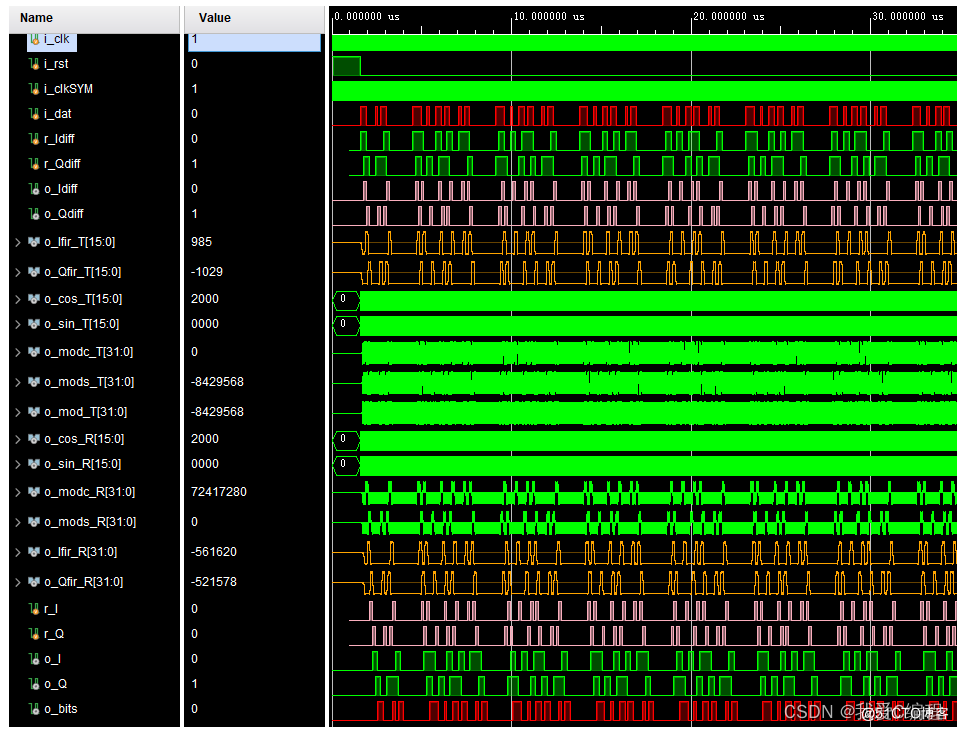

m基于FPGA的costas环载波同步verilog实现,包含testbench,可以修改频偏大小

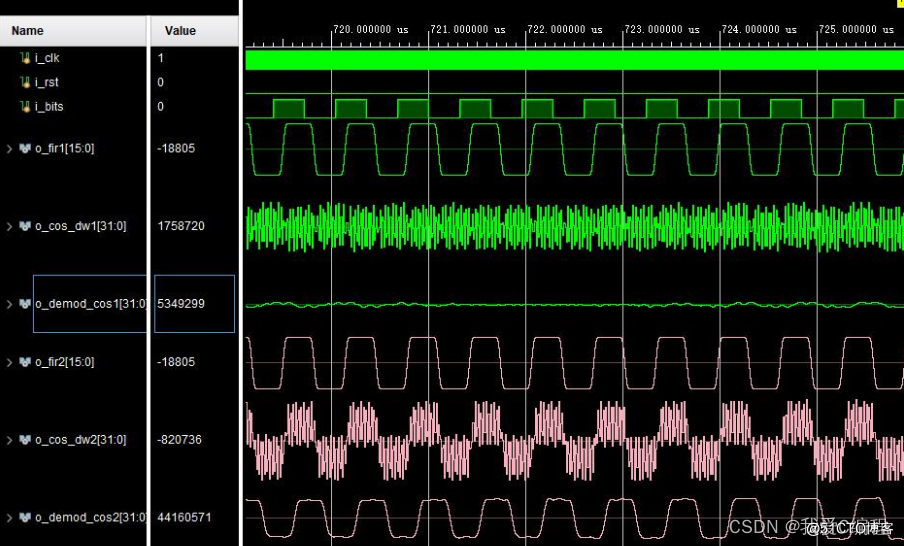

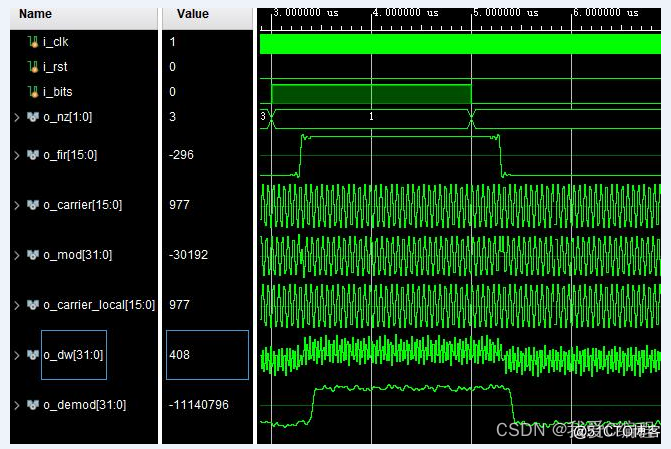

1.算法仿真效果其中Vivado2019.2仿真结果如下: 没有costas环,频偏对基带数据的影响 加入costas环的基带数据 2.算法涉及理论知识概要 Costas环是一种用于载波同步的常见方法,特别是在调制解调中,它被广泛用于解调相位调制信号,如二进制调相(BPSK)或四进制调相(QPSK)...

m基于FPGA的64QAM调制解调通信系统verilog实现,包含testbench,不包含载波同步

1.算法仿真效果 本系统进行了两个平台的开发,分别是: Vivado2019.2 Quartusii18.0+ModelSim-Altera 6.6d Starter Edition 其中Vivado2019.2仿真结果如下: 仿真结果导入matlab可以看星座图: Quartusii18.0+Mo...

m基于FPGA的DQPSK调制解调通信系统verilog实现,包含testbench,不包含载波同步

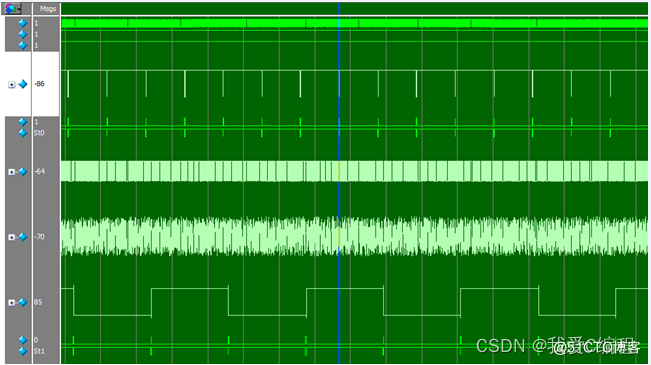

1.算法仿真效果 本系统进行了两个平台的开发,分别是: Vivado2019.2 Quartusii18.0+ModelSim-Altera 6.6d Starter Edition 其中Vivado2019.2仿真结果如下: 将上面的各个信号放大,各个信号含义如下: Quartusii18.0+M...

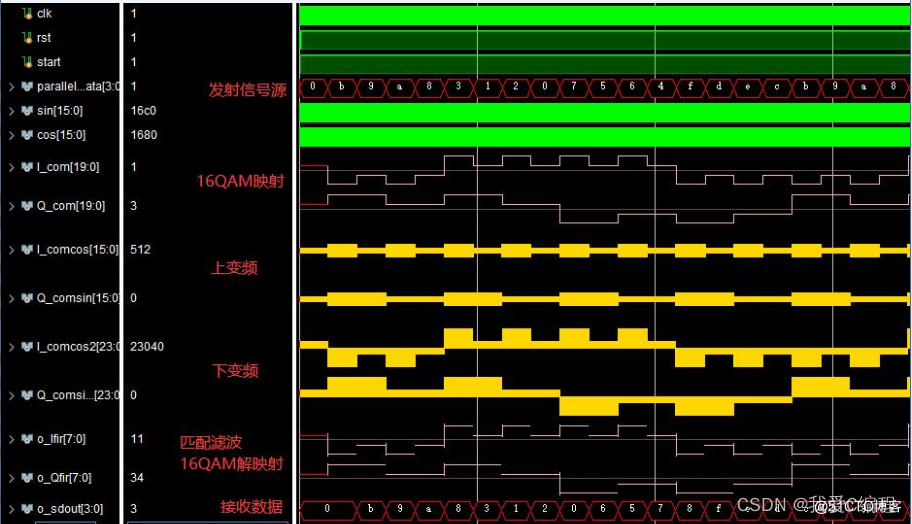

m基于FPGA的16QAM调制解调通信系统verilog实现,包含testbench,不包含载波同步

1.算法仿真效果本系统进行了两个平台的开发,分别是: Vivado2019.2 Quartusii18.0+ModelSim-Altera 6.6d Starter Edition 其中Vivado2019.2仿真结果如下: Quartusii18.0+ModelSim-Altera 6.6d St...

m基于FPGA的QPSK调制解调通信系统verilog实现,包含testbench,不包含载波同步

1.算法仿真效果 本系统进行了两个平台的开发,分别是: Vivado2019.2 Quartusii18.0+ModelSim-Altera 6.6d Starter Edition 其中Vivado2019.2仿真结果如下: Quartusii18.0+ModelSim-Altera 6.6d S...

m基于FPGA的BPSK调制解调通信系统verilog实现,包含testbench,包含载波同步

1.算法仿真效果vivado2019.2仿真结果如下: 对比没载波同步和有载波同步的仿真效果,我们可以看到,当不存在载波同步时,数据的包络会有一个缓慢的类正弦变换,这是由于存在频偏导致的。而当加入载波同步之后,数据的包络会存在少量起伏,但数据反转的情况已经没有了, 说明频偏得到了补偿。 2.算法涉及...

m基于FPGA的BPSK调制解调通信系统verilog实现,包含testbench,不包含载波同步

1.算法仿真效果本系统进行了两个平台的开发,分别是: Vivado2019.2 Quartusii18.0+ModelSim-Altera 6.6d Starter Edition 其中Vivado2019.2仿真结果如下: Quartusii18.0+ModelSim-Altera 6.6d St...

基于FPGA的直接序列扩频通信verilog设计,包括汉明编译码,扩频解扩,同步模块以及testbench

1.算法描述 与很多的通信技术类似,扩频技术最初也应用于保密通信和制导系统等军事技术。除了在军事通信中的应用,扩频技术在无线通信领域也有发展。目前扩频通信技术已经在测距、卫星通信、GPS导航定位、移动通信、电子对抗、跟踪、遥控和蓝牙技术等方面广泛应用。扩频通信技术具有很多独特的优点:具有抗干扰能力强...

m基于FPGA的64QAM调制解调、载波同步verilog实现

1.算法描述 64QAM(正交幅度调制),在使用同轴电缆的网络中,这种数字频率调制技术通常用于发送下行链路数据。64QAM在6mhz信道中,64QAM的传输速率非常高,最多可支持38.015mbps的峰值传输速率。然而,它对干扰信号很敏感,难以适应嘈杂的上行链路传输(从电缆用户到互联网)。参见QPS...

本页面内关键词为智能算法引擎基于机器学习所生成,如有任何问题,可在页面下方点击"联系我们"与我们沟通。

产品推荐

社区圈子

FPGA云服务器您可能感兴趣

- FPGA云服务器器件

- FPGA云服务器信号处理

- FPGA云服务器技术

- FPGA云服务器实例

- FPGA云服务器编程

- FPGA云服务器应用

- FPGA云服务器逻辑

- FPGA云服务器辅助

- FPGA云服务器信号发生器

- FPGA云服务器波形

- FPGA云服务器verilog

- FPGA云服务器testbench

- FPGA云服务器matlab

- FPGA云服务器测试

- FPGA云服务器模块

- FPGA云服务器文件

- FPGA云服务器验证

- FPGA云服务器驱动

- FPGA云服务器实验

- FPGA云服务器教程

- FPGA云服务器算法

- FPGA云服务器图像

- FPGA云服务器调制

- FPGA云服务器系统

- FPGA云服务器阿里云

- FPGA云服务器芯片

- FPGA云服务器程序

- FPGA云服务器信号

- FPGA云服务器硬件