m基于FPGA的GPS收发系统开发,包括码同步,载波同步,早迟门跟踪环,其中L1采用QPSK,L2采用BPSK

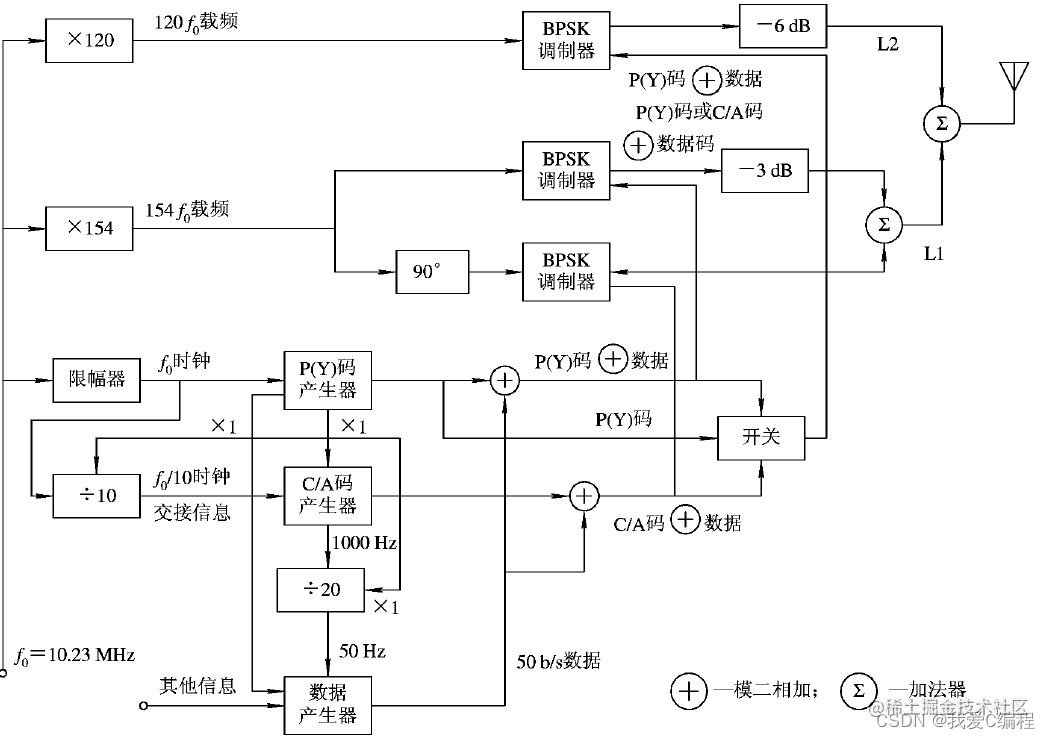

1.算法描述 最早的GPS包含L1和L2两个频段,其中L1上调制CA码,P码以及导航电文,L2上调制P码和导航电文。在实际接收到的GPS信号中,我们除了能够接受到CA码和P码外,还能检测到L1和L2两种载波信号。GPS双频发送器的基本构架如下所示: 使用CA码和P码两种码来区分双频道中的两种不同的频...

FPGA设计8位十进制计数器异步/同步模块以及m序列码产生器模块

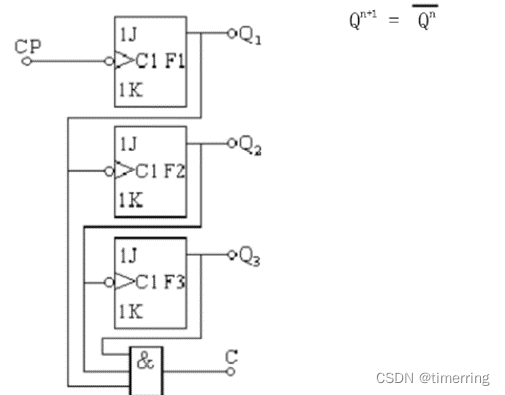

【实验三】设计一个8位十进制计数器(异步/同步)模块实验内容与原理说明根据计数器的构成原理,必须由四个触发器的状态来表示一位十进制数的四位二进制编码。而四位编码总共有十六个状态。所以必须去掉其中的六个状态,至于去掉哪六个状态,可有不同的选择。这里考虑去掉1010~1111六个状态,即采用8421B...

FPGA设计8位异步、同步二进制计数器

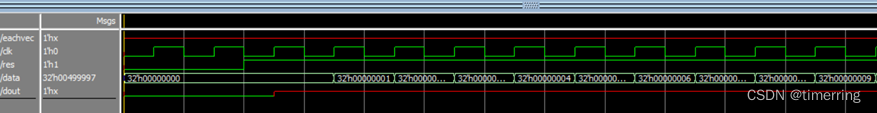

【实验要求】 实验内容与原理说明(包括框图、逻辑表达式和真值表)。实验模块程序代码(设计模块Design Block)和激励代码(激励模块Test Bench)。仿真波形图。综合得到的门级电路图。实验结果分析及思考。每一次报告用Word文档提交,文件名:姓名_班级_第几次实验_学号。【实...

【黑金原创教程】【FPGA那些事儿-驱动篇I 】实验十五:FIFO储存模块(同步)

实验十五:FIFO储存模块(同步) 笔者虽然在实验十四曾解释储存模块,而且也演示奇怪的家伙,但是实验十四只是一场游戏而已。至于实验十五,笔者会稍微严肃一点,手动建立有规格的储存模块,即同步FIFO。那些看过《时序篇》的同学一定对同步FIFO不会觉得陌生吧?因为笔者曾在《时序篇》建立基于移位寄存器的同...

本页面内关键词为智能算法引擎基于机器学习所生成,如有任何问题,可在页面下方点击"联系我们"与我们沟通。

产品推荐

社区圈子