【ZYNQ】裸机 PS + PL 双网口实现之 LWIP 库文件修改

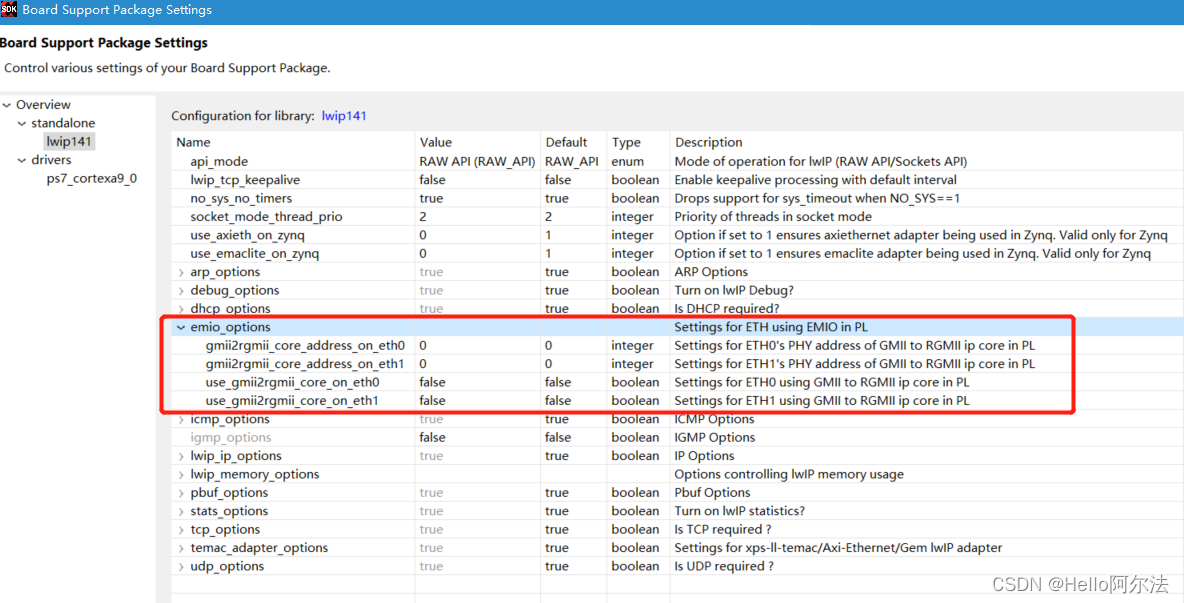

因项目需要,为实现 Zynq 裸机双网口通信功能,其中 ENET0 连接 PS 端网口,ENET1 通过 EMIO 扩展连接 PL 端网口,原 LWIP 库无板载 PHY 芯片支持及 EMIO 配置选项,故将 LWIP库文件进行修改以满足功能需求。 修改对象 Xilinx Vivado 2017.4...

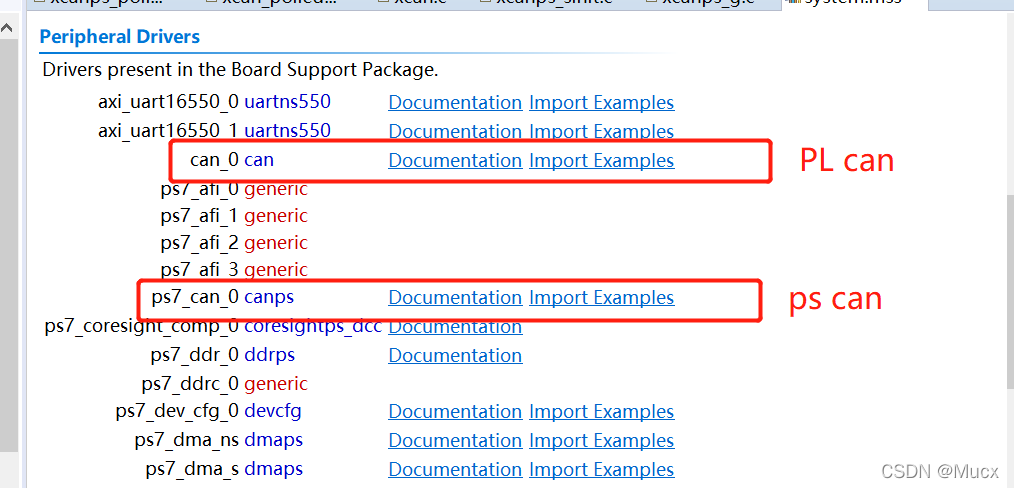

zynq 7000 sdk下裸机can(ps/pl) 调试

1. SDK下打开system.mss文件,如下图所示,import examples导入polled相关例程。因为我们的设备上有两个can,一个ps端一个pl端的,原理图在can收发器侧一样。2. ps 端参调试确定逻辑对ps can的clock配置值,为100M,参考《ug585-Zynq-70...

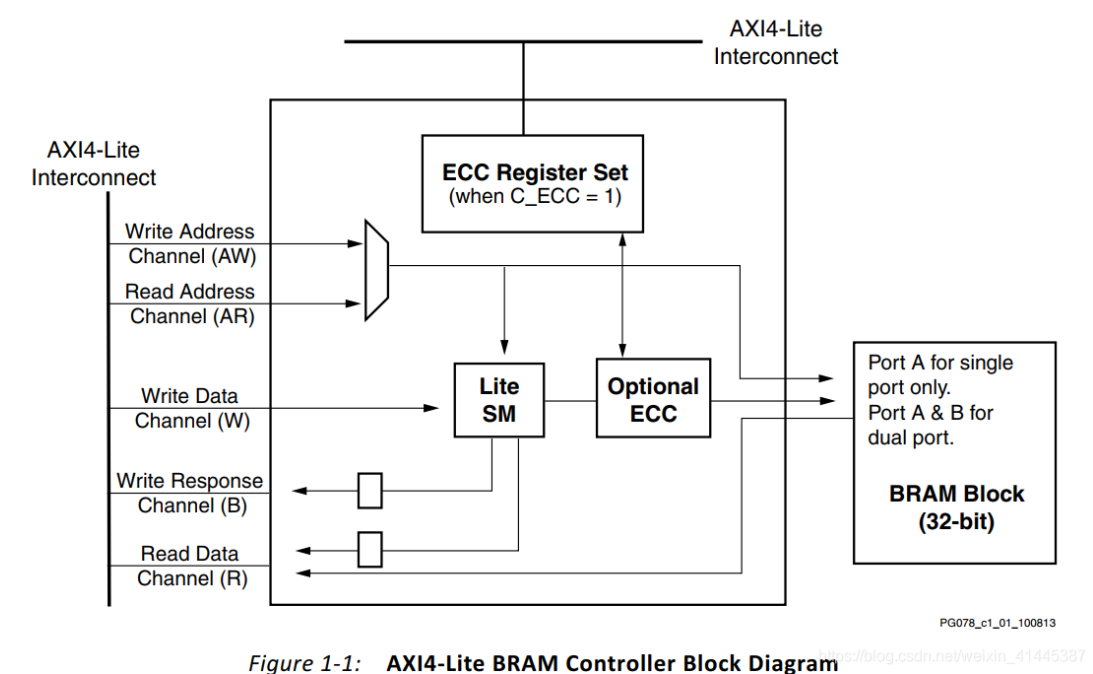

ZYNQ-基于BRAM的PS和PL数据交互

学习内容本文介绍关于AXI BRAM控制器的相关内容,针对数据量较少、地址不连续、长度不规则的情况,通过 BRAM 来进行数据的交互。开发环境vivado 18.3&SDK,PYNQ-Z2开发板。AXI BRAM控制器简介BRAM控制器可以用于与 AXI 互连和系统主设备的集成,以与本地块 ...

本页面内关键词为智能算法引擎基于机器学习所生成,如有任何问题,可在页面下方点击"联系我们"与我们沟通。